#### MAHARASHTRASTATE BOARD OF TECHNICAL EDUCATION (Autonomous)

(ISO/IEC - 27001 - 2013 Certified)

17659

#### <u>MODEL ANSWER</u> WINTER- 18 EXAMINATION

### **Subject Title:**Very Large Scale Integration

Subject Code:17659

#### **Important Instructions to examiners:**

- 1) The answers should be examined by key words and not as word-to-word as given in the model answer scheme.

- 2) The model answer and the answer written by candidate may vary but the examiner may try to assess the understanding level of the candidate.

- 3) The language errors such as grammatical, spelling errors should not be given more Importance (Not applicable for subject English and Communication Skills.

- 4) While assessing figures, examiner may give credit for principal components indicated in the figure. The figures drawn by candidate and model answer may vary. The examiner may give credit for any equivalent figure drawn.

- 5) Credits may be given step wise for numerical problems. In some cases, the assumed constant values may vary and there may be some difference in the candidate's answers and model answer.

- 6) In case of some questions credit may be given by judgement on part of examiner of relevant answer based on candidate's understanding.

- 7) For programming language papers, credit may be given to any other program based on equivalent concept.

| Q.<br>No. | Sub<br>Q.N. | Answe                                                                                                                                                                                                                                                          | er                                                                                                     |                                                                                                                                                                                   | Markin<br>g<br>Scheme                                                                                                                                    |

|-----------|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|

| Q.1       |             | Attempt any THREE:                                                                                                                                                                                                                                             |                                                                                                        |                                                                                                                                                                                   | 12-<br>Total<br>Marks                                                                                                                                    |

|           | 1)          | Comp                                                                                                                                                                                                                                                           | are Asynchronous sequential and syn                                                                    | chronous sequential circuits.                                                                                                                                                     | <b>4M</b>                                                                                                                                                |

|           |             | SR.<br>NO.                                                                                                                                                                                                                                                     | ASYNCHRONOUS<br>SEQUENTIAL CIRCUIT                                                                     | SYNCHRONOUS SEQUENTIAL CIRCUITS.                                                                                                                                                  |                                                                                                                                                          |

|           | Ans:        | 1                                                                                                                                                                                                                                                              | Output can be changed at any instant of time by changing the input                                     | Output changes at discrete interval of time                                                                                                                                       |                                                                                                                                                          |

|           |             | 2                                                                                                                                                                                                                                                              | The status of memory element will change any time as soon as input is changed. It does not use a clock | The status of memory is affected only at the active edge of clock, if input is changed. It uses a clock pulse.                                                                    | Each                                                                                                                                                     |

|           |             | 3                                                                                                                                                                                                                                                              | These circuits are easy to design                                                                      | These circuits are difficult to design.                                                                                                                                           | point 1                                                                                                                                                  |

|           |             | 4                                                                                                                                                                                                                                                              | They are slower as compare to synchronous.                                                             | They are faster as compare to asynchronous.                                                                                                                                       | mark                                                                                                                                                     |

|           |             |                                                                                                                                                                                                                                                                | 5                                                                                                      | Asynchronous is wherein all the flip-<br>flops within the counter do not<br>change state simultaneously. This is<br>because all the flip-flops are not<br>clocked simultaneously. | Synchronous is wherein all the flip-flops within the counter change state simultaneously. This is because all the flip-flops are clocked simultaneously. |

|           | 2)          | Explai                                                                                                                                                                                                                                                         | in estimation of channel capacitance of                                                                | of CMOS.                                                                                                                                                                          | 4M                                                                                                                                                       |

|           | Ans:        | Capacitance estimation: The dynamic response i.e. switching speed of MOS system depends on capacitance associated with the MOS devices which are formed by different layers in MOS transistors and interconnection capacitances that are formed by metal, poly |                                                                                                        |                                                                                                                                                                                   |                                                                                                                                                          |

(Autonomous) (ISO/IEC - 27001 - 2013 Certified)

and diffusion wires.

The total load capacitance on the output of a CMOS gate is the sum of:

- Gate capacitance of other inputs connected to the output of the gate.

- Diffusion capacitance of the drain connected to the output.

- Routing capacitance i.e. capacitance of interconnects between the output and other inputs.

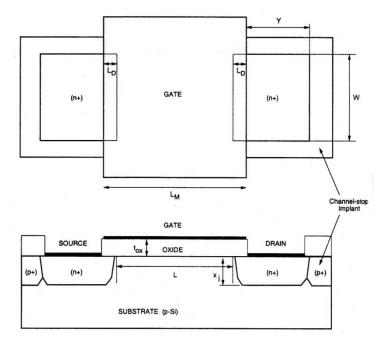

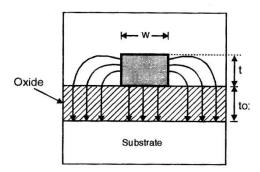

**MOSFET Capacitance:** The cross section view and top view of n channel MOSFET is as shown:

The mask length of the gate is indicated by  $L_M$  and the actual channel length is L. The extent of both the gate-source and the gate-drain overlaps are  $L_D$ .

Hence Channel length  $L = L_M - 2L_D$ .

The source and drain overlap region lengths are usually equal to each other because of the symmetry of the MOSFET structure. Generally  $L_D$  is of order of  $0.1\mu m$ . Both the source and drain diffusion regions have a width of W. The diffusion region length is denoted by y. These regions surrounded by p+ channel stops implants as it avoids formation of unwanted channels between the two neighboring n+ diffusions. Most of the parasitic device capacitances are due to three dimensional, distributed charge voltage relations within the device structure.

The parasitic device capacitances are of two types:

nces

Each 2 marks

(Autonomous) (ISO/IEC - 27001 - 2013 Certified)

1. Oxide related capacitances: The two capacitances that occur as a result of overlapping regions of source and drain are called  $C_{GD \, (overlap)}$  and  $C_{GS \, (overlap)}$  respectively:

$C_{GD \text{ (overlap)}} = C_{OX}$ . W.  $L_D$

$C_{GS \text{ (overlap)}} = C_{OX}$ . W.  $L_D$

With

$$C_{OX} = \frac{\epsilon_{OX}}{t_{OX}}$$

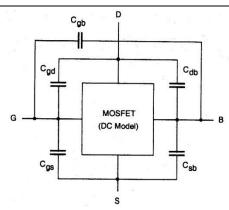

Both of these capacitances do not depend upon the bias condition that is they are voltage independent. Consider the capacitance that result from the interaction between the gate voltage and the channel charge. As the channel region is connected to the source, drain and substrate there are three capacitances between the gate and these regions:  $C_{GS}$ ,  $C_{GD}$ , and  $C_{GB}$  respectively.

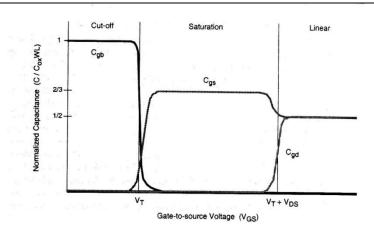

The gate of channel capacitance is distributed and voltage dependent. The gate to source capacitance is actually the gate to channel capacitance between the gate and the source terminals, the gate to drain capacitance is the gate to channel capacitance between the gate and drain terminal. As these capacitances are voltage dependent these capacitances are determined in different biasing conditions during cut-off, linear and saturation modes:

- In cut off mode surface is not inverted. There is no conducting channel that links the surface to the source and drain. Hence the gate to source and gate to drain capacitances:  $C_{gs} = C_{gd} = 0$ . Hence the gate to substrate capacitance can be approximated as:  $C_{gb} = C_{ox}.W.L$

- In linear mode of operation, the inverted channel extends across MOSFET, between the source and drain as shown. This conducting inversion layer on the surface effectively shields the substrate from the gate electric field, hence  $C_{gb} = 0$ . In this case the distributed gate to channel capacitance is shared between source and drain and is

given as:

$$C_{gs} = C_{gd} = \frac{1}{2}.C_{OX}.W.L$$

• In saturation mode, the inversion layer on the surface does not extend to the drain, but is pinched off. The gate to drain capacitance is hence equal to zero. As the source is still linked to the conducting channel, its shielding effect also forces the gate to substrate capacitance to zero. Hence the distributed gate to channel capacitance as seen

between gate and source is given as:  $C_{gs} = \frac{2}{3} . C_{ox} . W . L$

To calculate total capacitance all the gate oxide capacitances are summed up.

(Autonomous) (ISO/IEC - 27001 - 2013 Certified)

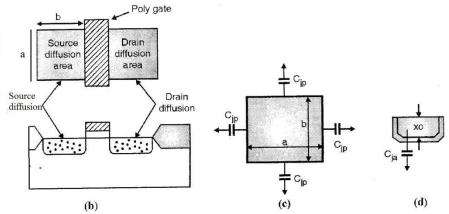

2. <u>Junction Capacitance</u>: Voltage dependent source substrate and drain substrate junction capacitances  $C_{sb}$  and  $C_{db}$  are formed due to the depletion charge surrounding the respective source to drain diffusion regions embedded in the substrate.

Both these junctions are reverse biased under normal operating conditions. These capacitances depend upon the voltage between the diffusion regions and substrate as well as on the effective area. The diffusion capacitance Cd is proportional to the total diffusion to substrate junctions area. There is a formation of base area and also of the area of the side wall periphery. The side wall capacitances can be characterized by a periphery capacitance per unit length.

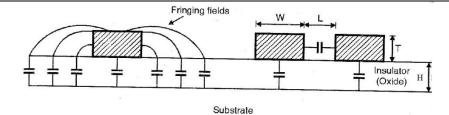

3. Routing Capacitance: As a metal layer is deposited on the insulating layer in the final stage of transistor fabrication capacitances are formed between the metal or poly layers and substrate. These capacitances are approximated using a parallel plate model:  $C = \frac{\varepsilon A}{t}$ . The parallel plate approximation however ignores fringing fields that occurs at the edges of conductor due to its finite thickness. If two conductors are running in parallel a

conductor can exhibit capacitance to an adjacent conductor on the same layer as shown:

(Autonomous) (ISO/IEC - 27001 - 2013 Certified)

To determine the routing capacitance the model is considered which is a simple isolated interconnect line:

The interconnect line has a length 1 and width W and thickness t. The line resistance can estimated as:  $R_{line} = R_x(l/w)$  ohms.

There is increase in parasitic resistance with length 1.

The total line capacitance can be estimated by using formula:  $C_{line} = \frac{\varepsilon_{ox} lw}{T_{ox}}$

$T_{ox}$  is the thickness of the insulating oxide between the line and substrate.

Cline is also called the self capacitance of line. But this equation ignores the fringing electric field from the edges and sides when the line is at a positive voltage.

Hence capacitance per unit length C that accounts for this effect is:

$$C = \varepsilon_{ox} \left[ 1.15 \left( \frac{W}{T_{ox}} \right) + 2.8 \left( \frac{t}{T_{ox}} \right)^{0.222} \right] \text{ F/cm.}$$

The first term accounts for fringing from the bottom side of the line, while the second terms depends on the thickness t and is due to the side wall effects.

|      | Draw CMOS two input NOR gate and write it's truth table.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | <b>4M</b>                                        |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------|

| Ans: |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Diagr<br>m = 3<br>mark<br>Trutl<br>table<br>mark |

|      | Truth table:           A         B         T1         T2         T3         T4         Y           0         0         OFF         OFF         ON         ON         Vdd           0         Vdd         ON         OFF         ON         O         O           Vdd         0         OFF         ON         ON         OFF         O                                                                                                                                                                                                               |                                                  |

| 4)   | Vdd Vdd ON ON OFF OFF 0  State any 4 features of VHDL.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 4M                                               |

| Ans: | 1. It is a concurrent language that is it can execute statements at same time in parallel as in hardware.  2. It is a sequential language that is it can execute sequential statements one at a time in sequence.  3. It supports synchronous and asynchronous timing models.  4. Facilitates device independent of design portability.  5. It supports design libraries.  6. It has well defined interface.  7. Behaviour specification for simulation purpose.  8. Test Benches can also be generated.  9. Digital modelling techniques supported. | Any 4<br>featur<br>1 mar<br>each                 |

|            | 17. Natu         | ord types: Define multiple signals into one ty<br>aral coding style for asynchronous resets.<br>ical statement (like case and if/then) endings | -                                                                    |                            |

|------------|------------------|------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------|----------------------------|

| <b>B</b> ) | Attemp           | t any ONE :                                                                                                                                    |                                                                      | 6                          |

| 1)         | Compa            | re FPGA and CPLD (any six pts).                                                                                                                |                                                                      | 6M                         |

|            | Sr<br>no:        | FPGA                                                                                                                                           | CPLD                                                                 |                            |

|            | 1.               | It is field programmable gate array.                                                                                                           | It is complex programmable logic device.                             |                            |

|            | 2.               | Capacity is defined in terms of number of gates available.                                                                                     | Capacity is defined in terms of number of macro cells available.     | Any 6 points = 1 mark each |

|            | 3.               | FPGA consumes less power than CPLD.                                                                                                            | CPLD consumes more power than FPGA                                   |                            |

| Ans:       | 4.               | Number of input and output pins on FPGA are less than CPLD.                                                                                    | Number of input and output pins on CPLD are more than FPGA.          |                            |

|            | 5.               | FPGA is suitable for designs with large number of blocks with few number of inputs.                                                            | CPLD is ideal for complex blocks with large number of inputs.        |                            |

|            | 6.               | FPGA based designs require more board space and layout is more complex.                                                                        | CPLD board designs need less board space and layout is less complex. |                            |

|            | 7.               | It is difficult to predict the speed performance of design.                                                                                    | Speed performance can be easily predicted.                           |                            |

|            | 8.               | FPGA are available in wide density range.                                                                                                      | CPLD contain fewer registers but have better performance.            |                            |

| 2)         | State ar         | ny one process for wafer fabrication with c                                                                                                    | liagram                                                              | 6M                         |

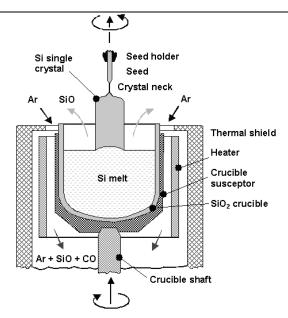

|            | The bas          | Processing: sis raw material used is a disk of silicon, we rand is less than 1mm thick used in semi-con                                        |                                                                      | Diagra<br>m = 2<br>marks   |

| Ans:       | pure mo          | are cut from ignots of silicon crystal that habiten polysilicon silicon. This method is know                                                   | vn as Czochralski [C-Z] method.                                      | Proces                     |

|            | {An ing processi | tot is a piece of material, usually metal, that is ing?                                                                                        | s cast into a shape suitable for further                             | -<br>4mark                 |

### MAHARASHTRASTATE BOARD OF TECHNICAL EDUCATION (Autonomous)

(ISO/IEC - 27001 - 2013 Certified)

For getting crystals with required electrical properties controlled amounts of impurities are added to the melt. To initiate single-crystal growth, the crystal orientation is determined by seed crystal is dipped into the melt and slowly pulled out. As the seed crystal is pulled out of the melt, it brings with it a solidified mass of silicon with the same crystalline structure as that of the seed.

During the crystal pulling process, the seed crystal and the crucible are rotated in opposite direction in order to produce ingots of circular cross- section. The diameter of the ingot is controlled by pulling rate and melt temperature. Ingot diameter is about 10 to 15 cm and length of order 100 cm. The ignot is also ground flat slightly to get reference plane. The ignot is then sliced using a stainless steel blade with industrial diamonds embedded into inner diameter cutting edge. This produces circular wafers of slices.

The silicon wafers obtained have very rough surface due to slicing operation. These wafers undergo a number of polishing steps to produce a flat surface.

Then one side of wafer is given a fine mirror smooth highly polished finish, where as the other side is simply lapped on an abrasive lapping machine to obtain acceptable degree of flatness. Finally the wafers are thoroughly rinsed and dried. A raw of thickness about 0.6 to 1mm produces wafer of about 0.15 to 0.8 mm thickness after all polishing steps.

#### OR

It consists of Quartz crucible, which is surrounded by a graphite radiator. The graphite is heated by radio frequency induction heating and temperature maintained a few degrees above the melting point of silicon (approx. 1425°C), the atmosphere just above the polysilicon melt is typically helium or orgon for freezing.

A polycrystalline Si is melted in the crucible and controlled amount of impurities (p type or n type) are added to the melt to provide the crystal with required electrical properties.

After the seed (single crystal silicon piece) is dipped into the melt, the seed is gradually withdrawn vertically from the melt while simultaneously being rotated. The molten polycrystalline silicon melts the tip of the seed and it is withdrawn, refreezing occurs. As the melt freezes, it assumes the single crystal form of the seed. This process is continued until the melt is consumed. The diameter of the ingot (rod of silicon) is determined by the seed withdrawn rate and seed rotation rate.

The produced crystalline silicon rod is then slicing into wafers using cutting tools like

|     |      | diamond blades. Following slicing at least one face of the wafer is polished to flat scratch free mirror finish surface.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                       |

|-----|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|

| Q 2 |      | Attempt any FOUR:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 16-<br>Total<br>Marks                 |

|     | 1)   | Explain fabrication using N-well process.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 4M                                    |

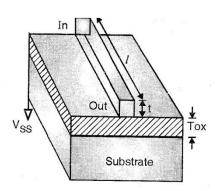

|     | Ans: | N-Well process: The N-well CMOS circuits are getting more popular because of the lower substrate bias effect on transistor threshold voltage and lower parasitic capacitances associated with source and drain regions.  The fabrication steps are as follows:  Thick SiO <sub>2</sub> layer is grown on p-type silicon wafer.  After defining the area for N-well diffusion, using a mask, the SiO <sub>2</sub> layer is etched off and n-well diffusion process is carried out.  Oxide in the n transistor region is removed and thin oxide layer is grown all over the surface to insulate gate and substrate.  The polysilicon is deposited and patterned on thin oxide regions using a mask to form gate of both the transistors. The thin oxide on source and drain regions of both the transistors is removed by proper masking steps.  Using n <sup>+</sup> mask and complementary n <sup>+</sup> mask, source and drain of both nMOS and pMOS transistors are formed one after another using respective diffusion processes. These same masks also include the V <sub>DD</sub> and V <sub>SS</sub> contacts.  The contacts are made using proper masking procedure and metal is deposited and patterned on the entire chip surface.  An overall passivation layer is formed and the openings for accessing bonding pads are defined. | Diagra m = 2 marks  Process = 2 marks |

|     | 2)   | Design Y=AB.CD using CMOS logic.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 4M                                    |

|      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | T              |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

| Ans: | <ul> <li>models to replicate how a device will perform in terms of timing and results. It should be performed at all stages of circuit design.</li> <li>Need of simulation: <ol> <li>VHDL simulation serves as a basis for testing complex designs and validating the design prior to fabrication.</li> <li>It allows the observation of the circuits behavior at the inputs and outputs and all internal rules.</li> <li>The simulation program processes as representation of input stimuli and determines the behavior of signal with respect to time stops.</li> <li>The simulation is done for the verification of the behavior of the circuit for both time behavior and fundamental behavior.</li> <li>Simulation operation can be used to verify independent delays in the circuits.</li> <li>Simulation is used for design verification: Validate assumptions, Verify logic, Verify performance (timing)</li> </ol> </li> </ul> | Definon = mark |

| Ans: | What do you mean by simulation? Why it is necessary?  Simulation is functional emulation of a circuit design through software programs that use                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 4M             |

|   |          |               | MOORE MACHIN                                                                           | E                                    | MELAY MACHINE                              |                   |

|---|----------|---------------|----------------------------------------------------------------------------------------|--------------------------------------|--------------------------------------------|-------------------|

|   |          |               |                                                                                        |                                      |                                            |                   |

|   |          | 1             | Output is function of                                                                  | state of machine.                    | Output is function of state of machine     |                   |

|   |          | 2             | Daguiras mara numb                                                                     | or of states                         | and present input condition.               |                   |

|   | <b>A</b> | $\frac{2}{3}$ | Requires more numb Faster.                                                             | er or states.                        | Requires less number of states.  Slower.   |                   |

|   |          | 4             | Simple design.                                                                         |                                      | Complex design.                            | Any 4             |

|   |          | 5             | Output in state.                                                                       |                                      | Output is at the time of state transition. | points =<br>1mark |

|   | Ans:     | 6             | Block diagram:                                                                         |                                      | Block diagram:                             | each              |

|   |          |               | present stat                                                                           | le                                   | present state                              | Cacii             |

|   |          |               |                                                                                        | next state                           | Combinational next state                   |                   |

|   |          |               | input — Combinational Logic                                                            | decode                               | _ inputLogic                               |                   |

|   |          |               |                                                                                        |                                      | output                                     |                   |

|   |          |               | <moo< td=""><td>re Machine&gt;</td><td><mealy machine=""></mealy></td><td></td></moo<> | re Machine>                          | <mealy machine=""></mealy>                 |                   |

|   |          |               |                                                                                        |                                      |                                            |                   |

|   | 5)       | Write VHI     | OL code for half adde                                                                  | er.                                  |                                            | <b>4M</b>         |

|   |          | Half adder w  | hich is having one XOR                                                                 | gate and a AND gate.                 |                                            |                   |

|   |          |               | A                                                                                      | 77                                   |                                            |                   |

|   |          |               | В                                                                                      |                                      | <b>—</b> s                                 |                   |

|   |          |               |                                                                                        |                                      |                                            |                   |

|   | Ans:     |               |                                                                                        | - 11                                 |                                            |                   |

|   |          |               |                                                                                        |                                      |                                            |                   |

|   |          |               |                                                                                        |                                      |                                            |                   |

|   |          |               |                                                                                        | · 니                                  | <b>-</b> c                                 |                   |

|   |          |               |                                                                                        |                                      |                                            |                   |

|   |          |               | Lil                                                                                    | orary IEEE;                          |                                            |                   |

|   |          |               | use                                                                                    |                                      |                                            | Code=4            |

|   |          |               | IEI                                                                                    | EE.STD_LOGIC_116                     | 54. <b>all</b> ;                           | marks             |

|   |          |               | ont                                                                                    | t <b>ity</b> ha_en is                |                                            |                   |

|   |          |               |                                                                                        | nty na_en is<br>rt (A,B:inbit;S,C:ou | thit):                                     |                   |

|   |          |               |                                                                                        | <b>d</b> ha_en;                      | -~,                                        |                   |

|   |          |               |                                                                                        | _ /                                  |                                            |                   |

|   |          |               |                                                                                        | chitecture ha_ar of h                | a_en <b>is</b>                             |                   |

|   |          |               | beg                                                                                    |                                      |                                            |                   |

|   |          |               |                                                                                        | S<=A xor B;                          |                                            |                   |

|   |          |               |                                                                                        | C<=A and B;                          |                                            |                   |

|   |          |               | ene                                                                                    | <b>d</b> ha_ar;                      |                                            |                   |

|   |          |               | <u> </u>                                                                               |                                      |                                            |                   |

|   |          | Note – Any    | relevant Code Marks                                                                    | to be given.                         |                                            |                   |

| , |          | A ++ 0 +      | w FOUD                                                                                 |                                      |                                            | 16-               |

| 3 |          | Attempt ar    | IY FUUK :                                                                              |                                      |                                            | Total<br>Marks    |

|   | 9)       | Write the s   | syntax of entity and a                                                                 | rchitecture used in `                | VHDL and explain it.                       | 4M                |

|   | a)       | , , , ,       |                                                                                        |                                      | · · · · · · · · · · · · · · · · · · ·      | 4111              |

|            | Entity declaration:                                                                                                                                                                                                                                                                                                                                                                             |                                       |

|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|

|            | It defines the names. Input output signals and modes of a hardware module. Also it provides the external interface of an entity. It is a black box view.                                                                                                                                                                                                                                        |                                       |

|            | Syntax: entity entity _ name is Port declaration. end entity_name                                                                                                                                                                                                                                                                                                                               | 1M<br>Explana<br>tion<br>1M<br>Syntax |

| Ans:       | Architecture: It describes the internal description of it tells what is thereinside design. Each entity has at least one architecture and an entity can have many architecture. Architecture can be described using structural, dataflow, behavioral or mixed style. Architecture can be used to described a design at different levels of abstraction like gate level (RTL) or behavior level. | Each                                  |

|            | Syntax: architecture architecture _name of entity_ name Architecture_ declaration_ name; begin Statement; end architecture_ name;                                                                                                                                                                                                                                                               |                                       |

| <b>b</b> ) | Draw 2:4 decoder and write VHDL code for it.                                                                                                                                                                                                                                                                                                                                                    | 4M                                    |

|            | (Note – Any relevant code with different statements marks to be given. Decoder with active high is also consider)                                                                                                                                                                                                                                                                               |                                       |

|            |                                                                                                                                                                                                                                                                                                                                                                                                 |                                       |

|            | library IEEE; use IEEE.STD_LOGIC_1164.all; entity decoder is                                                                                                                                                                                                                                                                                                                                    |                                       |

| Ans:       | use IEEE.STD_LOGIC_1164.all; entity decoder is port( a: in STD_LOGIC_VECTOR(1 downto 0) b: out STD_LOGIC_VECTOR(3 downto 0)); end decoder; architecture bhv of decoder is                                                                                                                                                                                                                       | 2M<br>Entity<br>2M<br>Architet        |

| Ans:       | use IEEE.STD_LOGIC_1164.all; entity decoder is port( a: in STD_LOGIC_VECTOR(1 downto 0) b: out STD_LOGIC_VECTOR(3 downto 0)); end decoder; architecture bhv of decoder is begin process(a) begin case a is                                                                                                                                                                                      | Entity<br>2M                          |

| Ans:       | use IEEE.STD_LOGIC_1164.all; entity decoder is port( a: in STD_LOGIC_VECTOR(1 downto 0) b: out STD_LOGIC_VECTOR(3 downto 0)); end decoder; architecture bhv of decoder is begin process(a) begin                                                                                                                                                                                                | Entity<br>2M<br>Architet              |

| <b>c</b> ) | Describe Twin-tube process with diagram.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 4M                    |

|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|

|            | Twin Tub Process:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                       |

|            | <ul> <li>A logical extension of the p-well and n-well approaches is the twin-tub fabrication process.</li> <li>In this process, a substrate of high resistivity of n-type material is used and then in this n-type material both n-well and p-well regions are created.</li> <li>By using this process, it is possible to preserve the performance of n-transistors without compromising the p-transistors.</li> <li>The doping control is more rapidly achieved and some relaxation is manufacturing tolerances results.</li> <li>This is particularly important as far as latch up is concerned.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 2M<br>Explana<br>tion |

| Ans:       | Note: step wise process is also suitably considered                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 2M<br>Diagra<br>m     |

| <b>d</b> ) | What do you meant by sensitivity list and zero modeling?                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 4M                    |

| Ans:       | Sensitivity list:  Every concurrent statement has a sensitivity list. Statements are executed only when there is an event or signal in the sensitivity list, otherwise they are suspended.  Ex. F<=a and b;  A and b are in the sensitivity list of f. the statement will execute only if one of these will change.  Ex. Proc ess(clk, RST)  The process is sensitive to RST and clk signal i.e. an event on any of these signals will cause the process toresume  Zero Modeling:  All digital circuit elements have a delay (propagation delay) which is very small in terms of nano sec. This nano sec delta delay will have little impact while writing the VHDL code. But for circuit realization this delay must be incorporated. The physical circuit always has finite delay. The ordering of zero delay events is handled with a fictitious unit called delta time. Delta time represents the execution of a simulation cycle without advancing Simulation time. The simulator models zero-delay events using delta time. Events scheduled at the same time are simulated in specific order during a delta time step. Related logic is then resimulated to propagate the effects for another delta timestep. Delta time steps continue until | 2M<br>Each            |

|     | <b>e</b> ) | Compare s            | signals and variables in VHDL                                                                             |                                                                                                | 4M                    |

|-----|------------|----------------------|-----------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|-----------------------|

|     |            | Sr.<br>No Signals    | Signals                                                                                                   | Variables                                                                                      |                       |

|     |            | 1                    | Signal objects are used to connect entities together to form models                                       | Variables are used for local storage in process statements and subprograms.                    |                       |

|     |            | 2                    | Signals have their values scheduled in the future                                                         | Variables have all assignments to variables occur immediately                                  | Any 4                 |

|     | Ans:       | 3                    | The keyword signal is followed by one or more signal names                                                | The keyword variable is followed by one or more variable names                                 | points<br>1M<br>each  |

|     |            | 4                    | Signals can be declared in entity declaration sections architecture declarations and package declarations | Variables can be declared in the process declaration and subprogram declaration sections only. |                       |

|     |            | 5                    | Signals need more information so more memory                                                              | Variables take less memory                                                                     |                       |

| Q.4 | <b>A</b> ) | Attempt a            | ny THREE :                                                                                                |                                                                                                | 12-<br>Total<br>Marks |

|     | 1)         | 1) 1<br>2) 1<br>3) 8 | following terms :<br>Noise margin<br>Power fanout<br>Skew<br>Meta stability                               |                                                                                                | 4M                    |

|     |            | It is a meas         |                                                                                                           | cuit (noise immunity is the ability of a gate without performing a wrong operation)            |                       |

|     | Ans:       |                      | ver fanout :                                                                                              |                                                                                                | 1M<br>each            |

|     |            |                      | ximum number of load gates that can mily and by maintaining its output wi  OR                             | be connected at output without loading with<br>thin the specified limit.                       |                       |

|     |            | The ability          | to drive the similar number of gates.                                                                     |                                                                                                |                       |

|      | The difference in the clock arrival time is call clock skew.  4) Meta stability:  Metastability in electronics is the ability of a non-equilibrium electronic state to persist for a long (and theoretically unboundable) period of time.  OR                                                                                                                                                                                                                                                                               |                                  |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|

|      | A metastable state is half way between logic "0" and logic "1" .It is undefined state.                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                  |

| 2)   | Explainevent scheduling with suitable example.                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 4M                               |

| Ans: | The assignment to signal x does not happen instantly. Each of the values assigned to x contain an afterclause.  The mechanism for delaying the new value is called scheduling an event. By assigning port x a new value, anevent was scheduled 0.5ns in the future that contains the new value forsignal x. when the event matures, signal receives a new value.  Event is nothing but change on target signal which is to be updated.  Example: X<= a after 0.5ns when select=0 else X<= b after 0.5ns                     | 2M<br>Expl<br>tion<br>2M<br>exan |

| 3)   | What is test bench? Write its applications  Test Bench:                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 4M                               |

|      | A test bench is used to verify the functionality of the design.  We need to stimulate our designs in order to test their functionality. Stimulus in a real system is from an external source, not from our design. We need a method to test our designs that is not part of the design itself. This is called a "Test Bench". Test Benches are VHDL entity/architectures. We initiate the design to be tested using components. We call these instantiations "Unit Under Test" (UUT) or "Device Under Test". The entity has | 2M<br>Expl<br>tion               |

| 3. It is used to analyze the design to compare the result of two simulations. 4. To compare the results of two simulations. 5. To apply this stimulus to the entity under test and to collect output responses. 6. To compare output responses with expected values.  4) List different concurrent statements and give the example of any two.  Concurrent Statements in VHDL  • With –select statement • When –else statement • Generate statement | 4M         |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

| 5. To apply this stimulus to the entity under test and to collect output responses. 6. To compare output responses with expected values.  4) List different concurrent statements and give the example of any two.  Concurrent Statements in VHDL  • With –select statement  • When –else statement                                                                                                                                                 | 4M         |

| 6. To compare output responses with expected values.  4) List different concurrent statements and give the example of any two.  Concurrent Statements in VHDL  • With –select statement  • When –else statement                                                                                                                                                                                                                                     | 4M         |

| 4) List different concurrent statements and give the example of any two.  Concurrent Statements in VHDL  With –select statement  When –else statement                                                                                                                                                                                                                                                                                               | 4M         |

| Concurrent Statements in VHDL  • With –select statement • When –else statement                                                                                                                                                                                                                                                                                                                                                                      | 4M         |

| <ul> <li>With –select statement</li> <li>When –else statement</li> </ul>                                                                                                                                                                                                                                                                                                                                                                            |            |

| When –else statement                                                                                                                                                                                                                                                                                                                                                                                                                                |            |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                     |            |

| Generate statement                                                                                                                                                                                                                                                                                                                                                                                                                                  |            |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                     |            |

| Block statement                                                                                                                                                                                                                                                                                                                                                                                                                                     |            |

| Note – Any Relevant Code using concurrent statements marks to be given, Only for the syntax with respect to example also marks to be given only architectural part is expected in example.                                                                                                                                                                                                                                                          |            |

| EXAMPLE 11                                                                                                                                                                                                                                                                                                                                                                                                                                          | 1M List    |

| 4:1 multiplexer using with-select statement.                                                                                                                                                                                                                                                                                                                                                                                                        |            |

| Library IEEE;                                                                                                                                                                                                                                                                                                                                                                                                                                       |            |

| Use IEEE. Std_logic_1164.all;                                                                                                                                                                                                                                                                                                                                                                                                                       |            |