(ISO/IEC - 27001 - 2005 Certified)

17659

# MODEL ANSWER

## SUMMER- 19 EXAMINATION

# Subject Title: Very Large Scale Integration

Subject Code: 17659

## **Important Instructions to examiners:**

- 1) The answers should be examined by key words and not as word-to-word as given in the model answer scheme.

- 2) The model answer and the answer written by candidate may vary but the examiner may try to assess the understanding level of the candidate.

- 3) The language errors such as grammatical, spelling errors should not be given more Importance (Not applicable for subject English and Communication Skills.

- 4) While assessing figures, examiner may give credit for principal components indicated in the figure. The figures drawn by candidate and model answer may vary. The examiner may give credit for anyequivalent figure drawn.

- 5) Credits may be given step wise for numerical problems. In some cases, the assumed constant values may vary and there may be some difference in the candidate's answers and model answer.

- 6) In case of some questions credit may be given by judgment on part of examiner of relevant answer based on candidate's understanding.

- 7) For programming language papers, credit may be given to any other program based on equivalent concept.

| Q.<br>No. | Sub<br>Q.N. | Answer                                 | Marking<br>Scheme |

|-----------|-------------|----------------------------------------|-------------------|

| Q.1       |             | Attempt any FIVE :                     | 20M               |

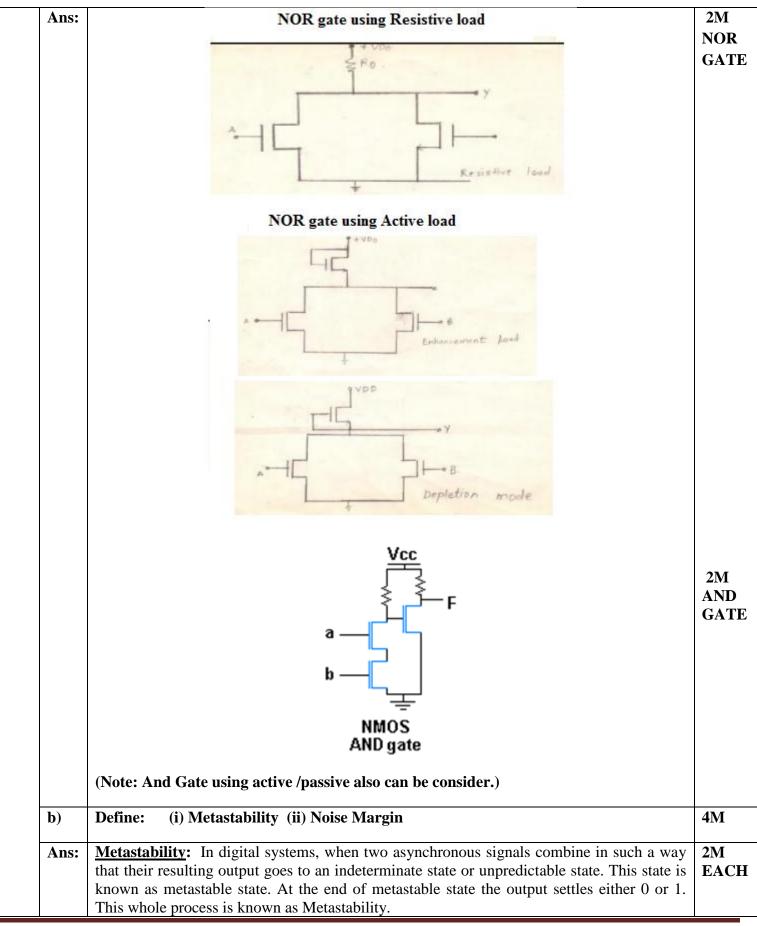

|           | a)          | Draw AND gate and NOR gate using NMOS. | <b>4</b> M        |

|      | <b><u>Noise Margins</u></b> : It is a measure of noise immunity of a gate or circuit (noise immunity is the ability of a gate or circuit to tolerate any noise present in a signal without |                                                                                                              |                                                                                                                        |                                    |  |  |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------|------------------------------------|--|--|

| c)   |                                                                                                                                                                                            | ming a wrong operation).                                                                                     |                                                                                                                        | <b>4</b> M                         |  |  |

| Ans: | · · ·                                                                                                                                                                                      |                                                                                                              |                                                                                                                        | EACH                               |  |  |

| ΑΠ5. | Sr.<br>No.                                                                                                                                                                                 | Moore Machine                                                                                                | Mealy Machine                                                                                                          | Point<br>1M                        |  |  |

|      | 1.                                                                                                                                                                                         | Moore machine is the sequential<br>system where output depends only on<br>present state.<br>f(o/p) = f(P.S.) | Mealy machine is the sequential<br>system where output depends on<br>present input and state.<br>f(o/p) = f(i/p, P.S.) | (Any 4)                            |  |  |

|      | 2.                                                                                                                                                                                         | It has more number of states than<br>mealy machine.                                                          | It is smaller.                                                                                                         |                                    |  |  |

| ļ    | 3.                                                                                                                                                                                         | It is faster.                                                                                                | It is slower than Moore machine.                                                                                       |                                    |  |  |

|      | 4.                                                                                                                                                                                         | The output is delayed in a Moore<br>machine. Output does not occur until<br>the next state changes.          | Output occurs in the same state by change in input.                                                                    |                                    |  |  |

| ļ    | 5.                                                                                                                                                                                         | Simple to design.                                                                                            | Complicated to design.                                                                                                 |                                    |  |  |

|      |                                                                                                                                                                                            | Orbrats to<br>the outside work                                                                               | The conside works                                                                                                      |                                    |  |  |

| d)   | What                                                                                                                                                                                       | is VHDL? Write two advantages of V                                                                           | HDL.                                                                                                                   | <b>4M</b>                          |  |  |

| Ans: |                                                                                                                                                                                            | •                                                                                                            | Language that can be used to model digital                                                                             | 2M                                 |  |  |

|      | -                                                                                                                                                                                          | stem at many levels of abstraction, rar                                                                      | nging from the algorithmic level to the gate                                                                           |                                    |  |  |

|      |                                                                                                                                                                                            |                                                                                                              |                                                                                                                        |                                    |  |  |

|      | Advar                                                                                                                                                                                      | as in hardware.                                                                                              | In execute statements at same time in parallel<br>n execute sequential statements one at a time<br>ous timing models.  | <sup>1</sup> ⁄2M<br>Each<br>(Any 4 |  |  |

|      | •                                                                                                                                                                                          | Facilitates device independent of desig<br>It supports design libraries.                                     | n portability.                                                                                                         |                                    |  |  |

|            | <ul> <li>It has well defined interface.</li> <li>Behaviour specification for simulation purpose.</li> <li>Test Benches can also be generated.</li> <li>Digital modelling techniques supported.</li> <li>It is not technology specific.</li> <li>VHDL has powerful construct language, constructs such as else if, with select, case, when etc.</li> <li>VHDL supports flexible design methodologies top-down, bottom-up or mixed.</li> <li>Strongly typed language:</li> <li>Dealing with signed and unsigned numbers is natural, and there's less chance of making a precision mistake or assigning a 16-bit signal to a 4-bit signal.</li> </ul> |            |

|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

|            | <ul> <li>Ability to define custom types:</li> <li>Record types: Define multiple signals into one type.</li> <li>Natural coding style for asynchronous resets.</li> <li>Logical statement (like case and if/then) endings are clearly marked.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                            |            |

| <b>e</b> ) | Explain: (i) Sensitivity list. (ii) Wait statement                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | <b>4</b> M |

| Ans:       | <ul> <li>i) Sensitivity List</li> <li>Every concurrent statement has a sensitivity list. Statements are executed only when there is an event or signal in the sensitivity list, otherwise they are suspended.</li> <li>Ex. F&lt;=a and b;</li> <li>A and b are in the sensitivity list of f. the statement will execute only if one of these will change.</li> <li>Ex. Proc</li> <li>ess(clk, RST)</li> <li>The process is sensitive to RST and clk signal i.e. an event on any of these signals will cause the process toresume</li> </ul>                                                                                                        | 2M<br>Each |

|            | <ul> <li>ii) Wait Statement –</li> <li>Wait statement suspends the execution of event or procedure until some conditions are met. If no condition is given, the process will never be reactivated again.</li> <li>wait on [sensitivity list]; eg. wait on clk; wait until [condition]; wait until clk="1"</li> </ul>                                                                                                                                                                                                                                                                                                                               |            |

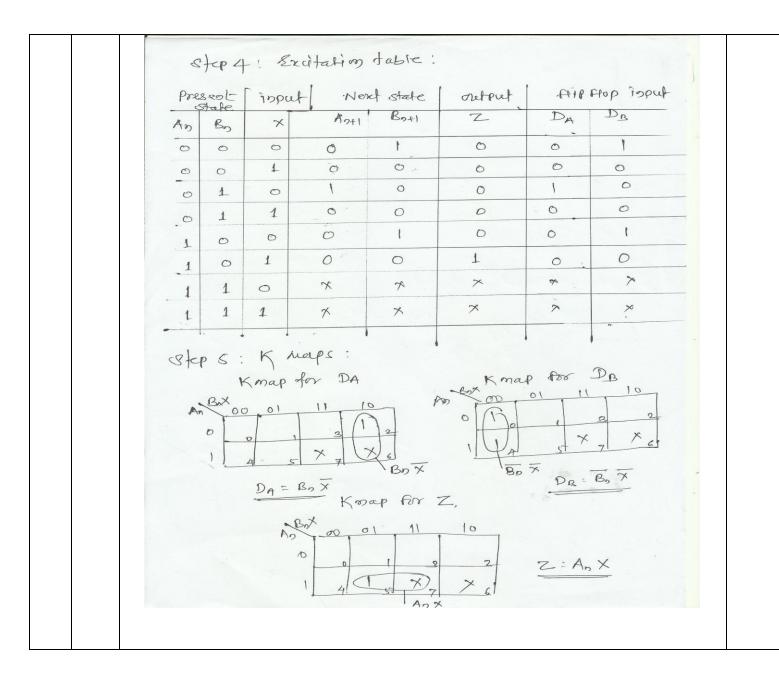

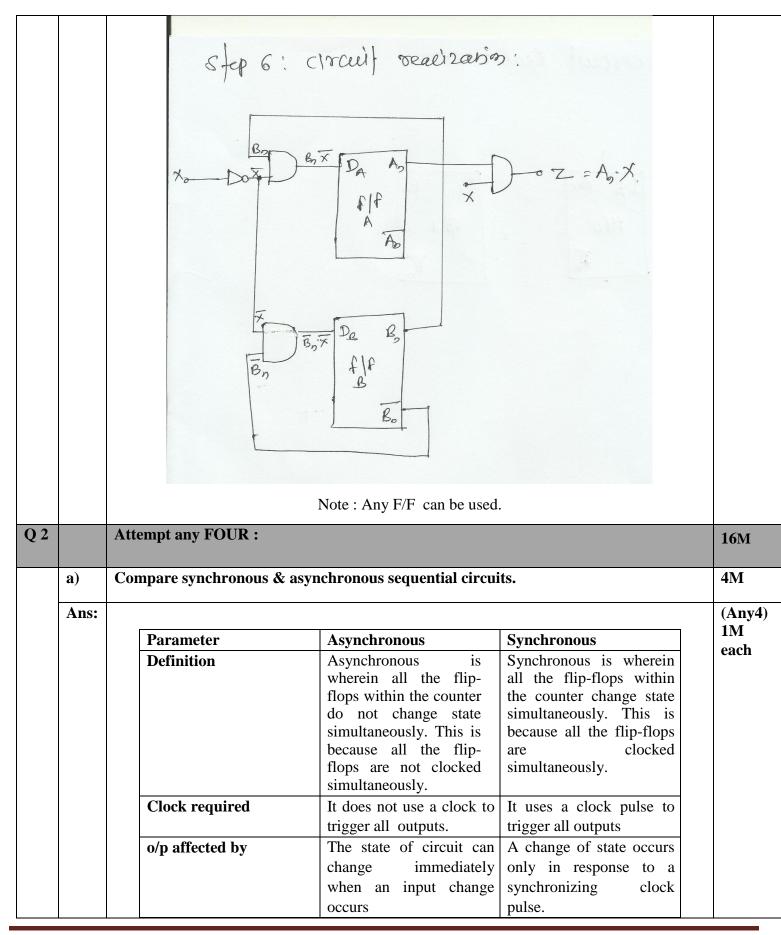

| Ans: | Step ! 1 : 8-ate Diagram<br>10 10 00<br>at 00 00<br>11<br>11<br>Step 2 : State Table : |        |

|------|----------------------------------------------------------------------------------------|--------|

|      | present Next state output (<br>state 2=0 2=1 2:0 2                                     |        |

|      | a ba o                                                                                 | 5      |

|      | b c a o a<br>c b a o                                                                   | 5<br>1 |

|      | Step 3: Modified Table<br>let a=00, b=01 of c=10<br>Membre,                            |        |

|      | present Nendistate output(z)<br>state 200 2=1 200 x=1                                  |        |

|      | ABABAB                                                                                 |        |

|      |                                                                                        |        |

|      | Μ      | lemory element                               | Either latches (u                   |            | Clocked FF                                         |

|------|--------|----------------------------------------------|-------------------------------------|------------|----------------------------------------------------|

|      | D      | aian                                         | FF) or logic gates<br>These circuit |            | These sinewite and easy to                         |

|      | D      | esign                                        | difficult to design                 |            | These circuits are easy to design.                 |

|      | C.     | aad                                          | e                                   | 1          |                                                    |

|      | 5      | peed                                         | They are faster                     |            | They are slower                                    |

|      |        |                                              | OR                                  |            |                                                    |

|      | SR.    | ASYNCHRONOU                                  | JS SEQUENTIAL                       | SYN        | NCHRONOUS SEQUENTIAI                               |

|      | NO.    |                                              | CUITS                               |            | CIRCUITS                                           |

|      | 1      | Output can be chang                          | •                                   | -          | hanges at discrete interval of                     |

|      |        | time by changing the                         |                                     | time       | 0 0 0 1 1                                          |

|      | 2      | The status of memor                          |                                     |            | is of memory is affected only                      |

|      |        | change any time as s<br>changed. It does not | -                                   | input is c | tive edge of clock, if                             |

|      |        | changed. It does not                         | use a clock                         |            | clock pulse.                                       |

|      | 3      | These circuits are ea                        | sy to design.                       |            | rcuits are difficult to design.                    |

|      | 4      | They are comparativ                          | · · ·                               |            | slower as clock is involved.                       |

|      | _      | clock is used .                              |                                     | a 1        |                                                    |

|      | 5      | Asynchronous is wh                           |                                     |            | nous is wherein all the swithin the counter change |

|      |        | flops within the course state simultaneously | 6                                   |            | ultaneously. This is because                       |

|      |        | the flip-flops are not                       |                                     |            | ip-flops are clocked                               |

|      |        | simultaneously.                              | clocked                             | simultan   |                                                    |

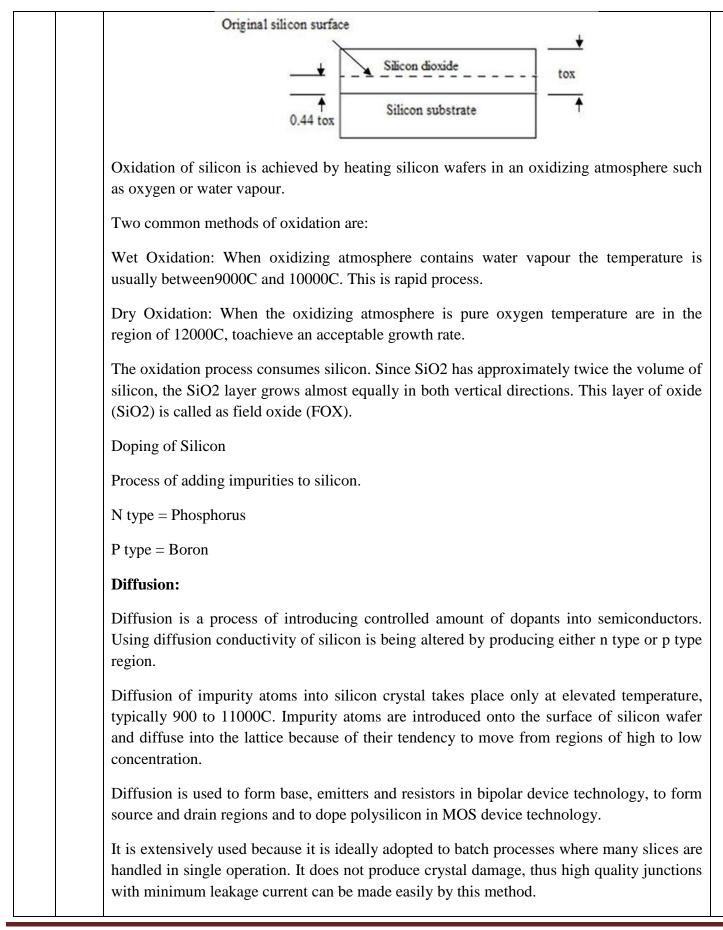

| b)   | Draw t | the architecture of sp                       | oaratan-3 FPGA seri                 |            |                                                    |

| Ans: | Archit | ecture :                                     |                                     |            |                                                    |

|      |        |                                              |                                     |            |                                                    |

|      |        | CLBs<br>CLBs<br>CLBs<br>CLBs<br>CLBs         |                                     |            |                                                    |

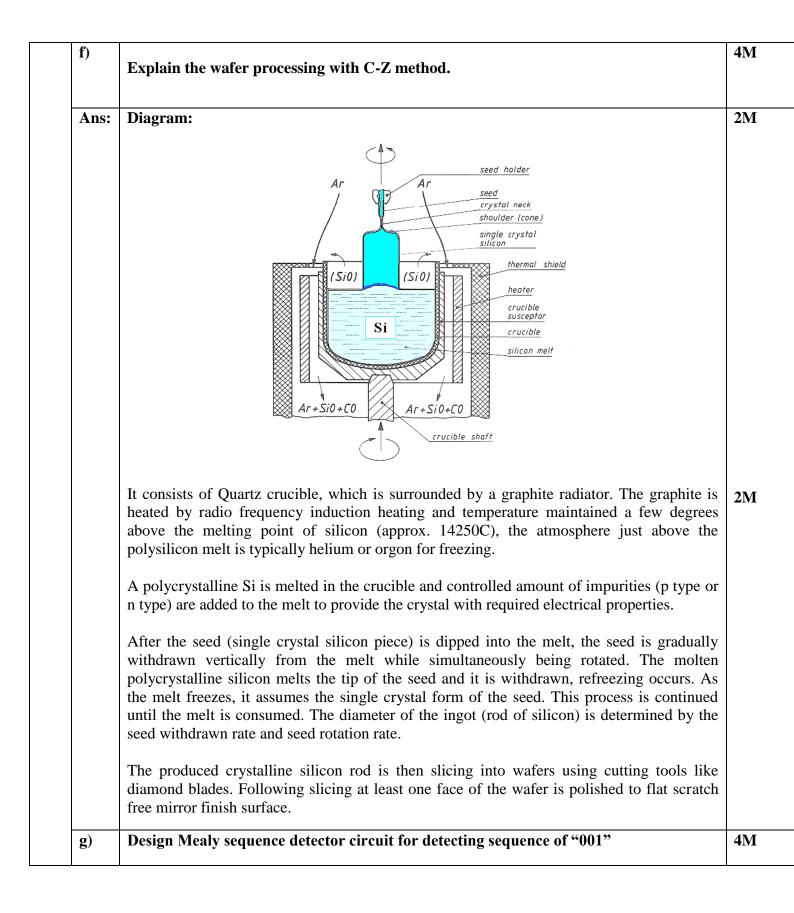

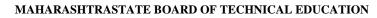

|            | The Spartan-3E family architecture consists of five fundamental programmable functional                                                      | Explai     |

|------------|----------------------------------------------------------------------------------------------------------------------------------------------|------------|

|            | elements:                                                                                                                                    | any 2      |

|            | Configurable Logic Blocks (CLBs): Contain flexible Look-Up Tables (LUTs) that                                                                | block      |

|            | implement logic plus storage elements used as flip-flops or latches. CLBs perform a wide variety of logical functions as well as store data. | 1M<br>Each |

|            | <b>Input/ Output Blocks (IOBs):</b> Control the flow of data between the I/O pins and the                                                    |            |

|            | internal logic of the device. Each                                                                                                           |            |

|            | IOB supports bidirectional data flow plus 3-state operation. Double Data-Rate (DDR) registers are included.                                  |            |

|            | Block RAM : Provides data storage in the form of 18-Kbit dual-port blocks.                                                                   |            |

|            | Multiplier Blocks : Accept two 18-bit binary numbers as inputs and calculate the product.                                                    |            |

|            | <b>Digital Clock Manager (DCM):</b> Blocks provide self-calibrating, fully digital solutions for                                             |            |

| <u>c)</u>  | distributing, delaying, multiplying, dividing, and phase-shifting clock signals.<br><b>Explain:</b> (i) Flattening (ii) Structuring          | 4M         |

| <b>c</b> ) | Explain: (1) Flattening (11) Structuring                                                                                                     | 4111       |

| Ans:       | Flattening:                                                                                                                                  | 2M         |

|            | The process of converting the optimized boolean description to a PLA format is known                                                         |            |

|            | ad flattening, because it creates a flat signal representation of only two levels: an AND                                                    |            |

|            | level and an OR level.                                                                                                                       |            |

|            | The idea is to get the unoptimized Boolean description into a format in which optimization                                                   |            |

|            | algorithms can be used to optimize the logic.                                                                                                |            |

|            | A PLA structure is a very easy description in which to perform boolean optimization, because                                                 |            |

|            | it has a simple structure and the algorithms are well known. An example of a Boolean                                                         |            |

|            | description is shown here:                                                                                                                   |            |

|            | Original equations                                                                                                                           |            |

|            | a=b  and  c;<br>b = x  or  (y  and  z);<br>c = q  or  w;<br>after flattering                                                                 |            |

|            | a = (x  or  (y  and  z))  and  (q  or  w);                                                                                                   |            |

|            | This description shows an output that has three equations describing its function. These                                                     |            |

|            | equations use two intermediate variables b and c to hold temporary values which are then                                                     |            |

|            | used to calculate the final value for a.                                                                                                     |            |

|            | These equations describe a particular structure of the design that contains two intermediate                                                 |            |

|            | nodes or signals b and c.                                                                                                                    | 2M         |

|            | The flattening process removes these intermediate nodes to produce a completely flat design with no intermediate nodes.                      |            |

|            | Structuring:<br>Structuring is the process of adding intermediate terms to add structure to a description.<br>Structuring is usually desirable as flattened designs are bigger and slower because of the<br>amount of fan-outs generated.<br>Example if [(a AND b) OR c] occurs ten times, then the tool may assign it a variable "x"                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                     |

|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|

|            | and then x is used everywhere.<br>Finally the sub functions are substituted into the original equations. Comparing to the logic before structuring, the resulting area is reduced.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                     |

| <b>d</b> ) | Write VHDL program for 3 : 8 decoder.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 4M                  |

| Ans:       | (Note Diagram is Optional)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Entity<br>1M        |

|            | A = 52 $B = 51$ $B$ | Archi<br>ture<br>3M |

|         | <b>Case 1:</b> When both the inputs A and B are at logic zero.<br>As inputs A' and B' are logic 1 both the n-MOS transistors $M_1$ and $M_2$ are at logic 1, they are ON. And both the switches are closed.<br>At the same time, p-MOS transistors $M_3$ and $M_4$ are OFF and both the switches are open.<br>As a result of which, the output is shorted to ground. Hence output $y = 0$ . (Logic 0) | Explain<br>OR |

|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|

|         | $y = A \cdot B$<br>Taking double bar<br>$y = \overline{A \cdot B}$<br>$y = \overline{A + B}$                                                                                                                                                                                                                                                                                                          |               |

| f) Ans: | Draw and explain CMOS AND gate.<br>Diagram:                                                                                                                                                                                                                                                                                                                                                           | 4M<br>2M      |

|         |                                                                                                                                                                                                                                                                                                                                                                                                       |               |

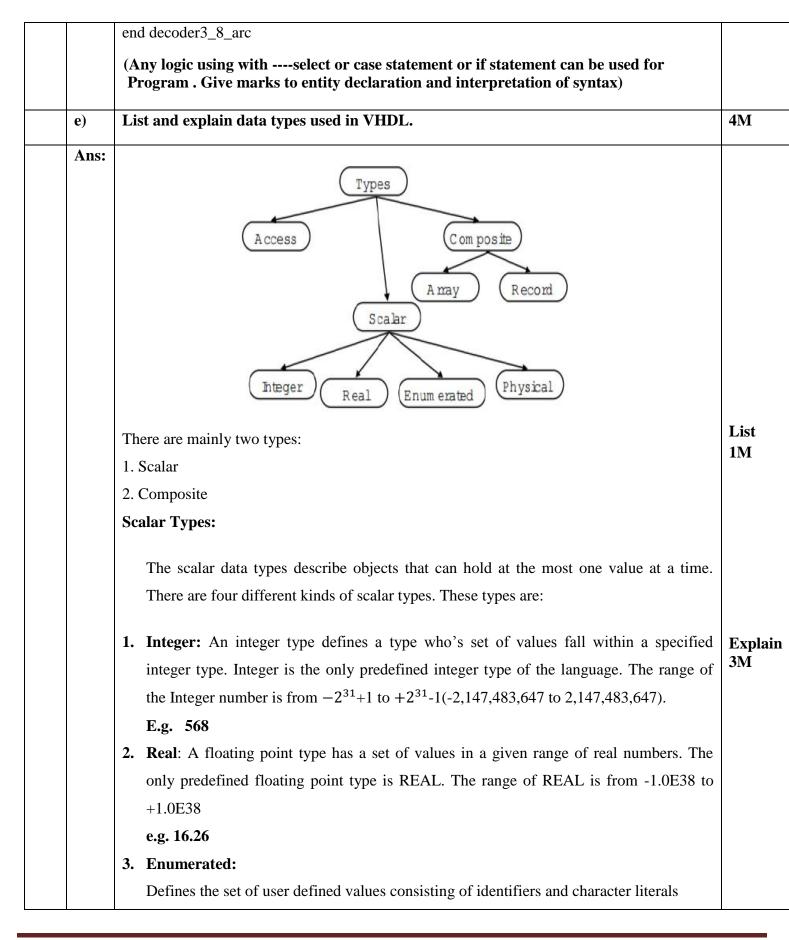

|         | <b>Record:</b> Contain elements of different types                                                                                                                                                                                                                                                                                                                                                    |               |

|         | A composite type represents a collection of values. There are two composite types:<br>Array: Contain many elements of same type.                                                                                                                                                                                                                                                                      |               |

|         | Composite data types:                                                                                                                                                                                                                                                                                                                                                                                 |               |

|         | <b>4. Physical:</b> A physical types are used to represent physical quantities such as length, voltage, time and current.                                                                                                                                                                                                                                                                             |               |

|         | The predefined enumeration types of the language are CHARACTER, BIT,<br>BOOLEAN, SEVERITY_LEVEL, FILE_OPEN_KIND and FILE_OPEN_STATUS.                                                                                                                                                                                                                                                                 |               |

|         | Type CAR_STATE is (STOP, SLOW, MEDIUM, FAST);                                                                                                                                                                                                                                                                                                                                                         |               |

|         | For example consider the following enumeration type declaration.                                                                                                                                                                                                                                                                                                                                      |               |

|         | This type values are represented by enumeration literals (either identifiers or character literals).                                                                                                                                                                                                                                                                                                  |               |

|     |      | <b>Case 3:</b> When A<br>As input A' =0 a<br>ON and M <sub>4</sub> is in<br>In the above two<br><b>Case 4:</b> When bo<br>As input A' =0 a<br>OFF and M <sub>4</sub> is in<br>In the above two<br>The working of 0 | above two conditions, the output is shorted to ground. Hence output $y = 0$ . (Logic 0)<br><b>1</b> : When both the inputs A and B are at logic 1.<br>but A' =0 and B'=0 transistor $M_1$ is OFF and transistor $M_3$ is ON and transistor $M_2$ is |                                                                                                                                                |                                                                                           |                                                     |                            |             |       | 2M        |

|-----|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|-----------------------------------------------------|----------------------------|-------------|-------|-----------|

|     |      |                                                                                                                                                                                                                    | Input                                                                                                                                                                                                                                               |                                                                                                                                                | CM                                                                                        | IOS                                                 |                            | Output      |       |           |

|     |      | А                                                                                                                                                                                                                  | B                                                                                                                                                                                                                                                   | M1                                                                                                                                             | M2                                                                                        | M3                                                  | M4                         | Juipui      |       |           |

|     |      | 0                                                                                                                                                                                                                  | 0                                                                                                                                                                                                                                                   | ON                                                                                                                                             | ON                                                                                        | OFF                                                 | OFF                        | 0           |       |           |

|     |      | 0                                                                                                                                                                                                                  | 1                                                                                                                                                                                                                                                   | ON                                                                                                                                             | OFF                                                                                       | OFF                                                 | ON                         | 0           |       |           |

|     |      | 1                                                                                                                                                                                                                  | 0                                                                                                                                                                                                                                                   | OFF                                                                                                                                            | ON                                                                                        | ON                                                  | OFF                        | 0           |       |           |

|     |      | 1                                                                                                                                                                                                                  | 1                                                                                                                                                                                                                                                   | OFF                                                                                                                                            | OFF                                                                                       | ON                                                  | ON                         | 1           |       |           |

| Q.3 |      | Attempt any FC                                                                                                                                                                                                     | OUR :                                                                                                                                                                                                                                               |                                                                                                                                                |                                                                                           |                                                     |                            |             |       | 16M       |

|     | a)   | List and explain                                                                                                                                                                                                   | features o                                                                                                                                                                                                                                          | f CPLD.                                                                                                                                        |                                                                                           |                                                     |                            |             |       | <b>4M</b> |

|     | Ans: | <ol> <li>Product t</li> <li>Typically</li> <li>Many ma</li> <li>Typically</li> <li>Minimum</li> <li>Routing I</li> </ol>                                                                                           | y one dedica<br>acrocells per<br>y all logic-b<br>n two logic-                                                                                                                                                                                      | ted flip-flop<br>logic-block<br>locks idention<br>blocks per o                                                                                 | o per macr<br>c<br>ca<br>levice                                                           | ocell                                               |                            |             |       | 4M        |

|     |      |                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                     |                                                                                                                                                | 0                                                                                         | R                                                   |                            |             |       |           |

|     |      | Logic D<br>2. In-Syste<br>3. Flexible<br>4. Fully Gr<br>5. 1 Static C<br>6. Power S<br>7. Program<br>8. Program                                                                                                    | evice.<br>m Program<br>Logic Mac<br>een (RoHS<br>Current<br>aving Optio<br>mable Pin-k<br>mable Schn<br>mable Input<br>ins Can Be<br>in Comme<br>d Digital CM<br>Fuse Featur                                                                        | ming (ISP)<br>rocell<br>Compliant)<br>n During Op<br>ceeper Option<br>tt Trigger<br>and I/O Pu<br>Configured<br>rcial and Ind<br>MOS Technolog | Supported<br>peration<br>on on Inpu<br>Option on<br>Il-up Opti<br>as Groun<br>dustrial Te | ts and I/O<br>Input and<br>on (per Pi<br>d (Optiona | s<br>I/O Pins<br>n)<br>al) | ex Programn | nable |           |

| b)   | State and explain delta delay.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | <b>4M</b>  |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

| Ans: | All digital circuit elements have a delay (propagation delay) which is very small in terms of nano sec. This nano sec delta delay will have little impact while writing the VHDL code. But for circuit realization this delay must be incorporated. The physical circuit always has finite delay. The ordering of zero delay events is handled with a fictitious unit called delta time. Delta time represents the execution of a simulation cycle without advancing Simulation time. The simulator models zero-delay events using delta time.Events scheduled at the same time are simulated in specific order during a delta time step.Related logic is then re-simulated to propagate the effects for another delta timestep. Delta time steps continue until there is no activity for the same instant of simulated time. | 41         |

|      | OR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |            |

|      | <b>Delta Delay:</b> The delta delay is introduced to achieve concurrency and order independence. The simulator freezes simulation time until all scheduled assignments in current simulation time is finished and there are no more events on the sensitivity list. Thus real and simulation time are different. Several logic changes occur simultaneously in a circuit. But a simulator cannot process events concurrently. Hence time is frozen within the time. Events are processed and logic values are updated one after another till no more events take place. This is known as one simulation cycle. The real time that the simulator takes to execute one simulation cycle is known as delta delay for simulation delta with zero simulation time.                                                                 |            |

| c)   | Write VHDL code for Full ADDER.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | <b>4</b> M |

| Ans: | A B Cin Cout                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 4M         |

|      | Library ieee;<br>use ieee.std_logic_1164.all;                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |            |

|      | entity full_adder is port(a,b,c:in bit; sum,carry:out bit);<br>end full_adder;                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |            |

|      | architecture data of full_adder is<br>begin<br>sum<= a xor b xor c;<br>carry <= ((a and b) or (b and c) or (a and c));                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |            |

|      | end data;                                                                                                                                                                                                                                                                                                                                                                                                             |            |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

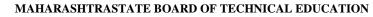

| d)   | Explain N-well process with diagram.                                                                                                                                                                                                                                                                                                                                                                                  | <b>4</b> N |

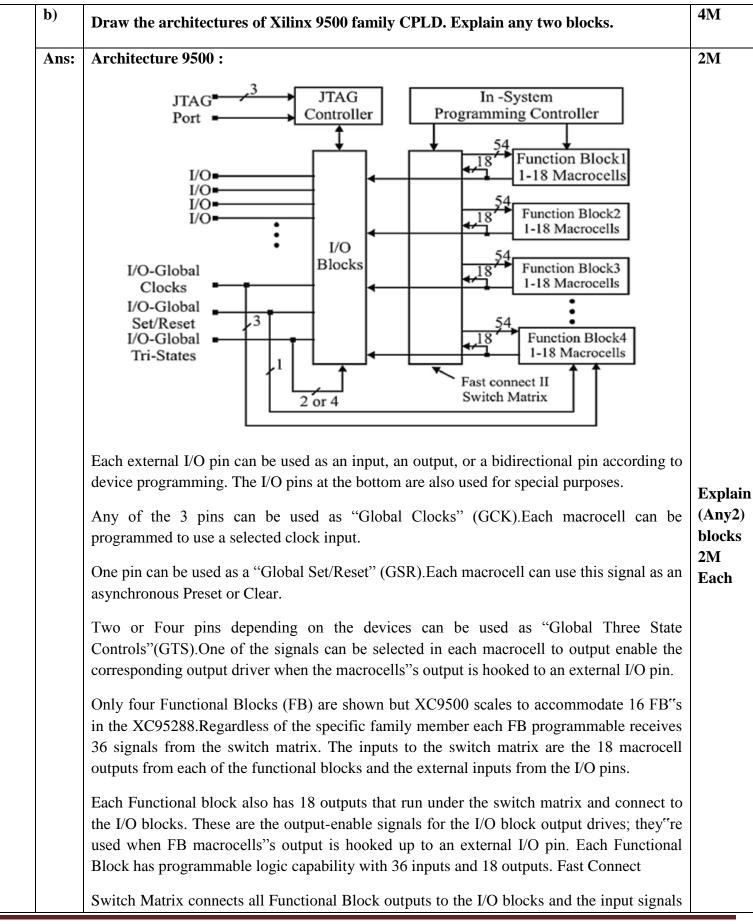

| Ans: | <u>N-Well process</u> : The N-well CMOS circuits are getting more popular because of the lower substrate bias effect on transistor threshold voltage and lower parasitic capacitances associated with source and drain regions.<br>$V_{DD} \circ V_{out}$                                                                                                                                                             | 4N         |

|      | n-well p substrate                                                                                                                                                                                                                                                                                                                                                                                                    |            |

|      | <ul> <li>Thick SiO<sub>2</sub> layer is grown on p-type silicon wafer.</li> <li>After defining the area for N-well diffusion, using a mask, the SiO<sub>2</sub> layer is etched off and n-well diffusion process is carried out.</li> </ul>                                                                                                                                                                           |            |

|      | <ul> <li>Oxide in the n transistor region is removed and thin oxide layer is grown all over the surface to insulate gate and substrate.</li> <li>The polysilicon is deposited and patterned on thin oxide regions using a mask to form gate of both the transistors. The thin oxide on source and drain regions of both the transistors is removed by proper masking steps.</li> </ul>                                |            |

|      | <ul> <li>Using n<sup>+</sup> mask and complementary n<sup>+</sup> mask, source and drain of both nMOS and pMOS transistors are formed one after another using respective diffusion processes. These same masks also include the V<sub>DD</sub> and V<sub>SS</sub> contacts.</li> <li>The contacts are made using proper masking procedure and metal is deposited and patterned on the entire chip surface.</li> </ul> |            |

|      | • An overall passivation layer is formed and the openings for accessing bonding pads are defined.                                                                                                                                                                                                                                                                                                                     |            |

| e)   | Explain Resistance Fabrication.                                                                                                                                                                                                                                                                                                                                                                                       | 4N         |

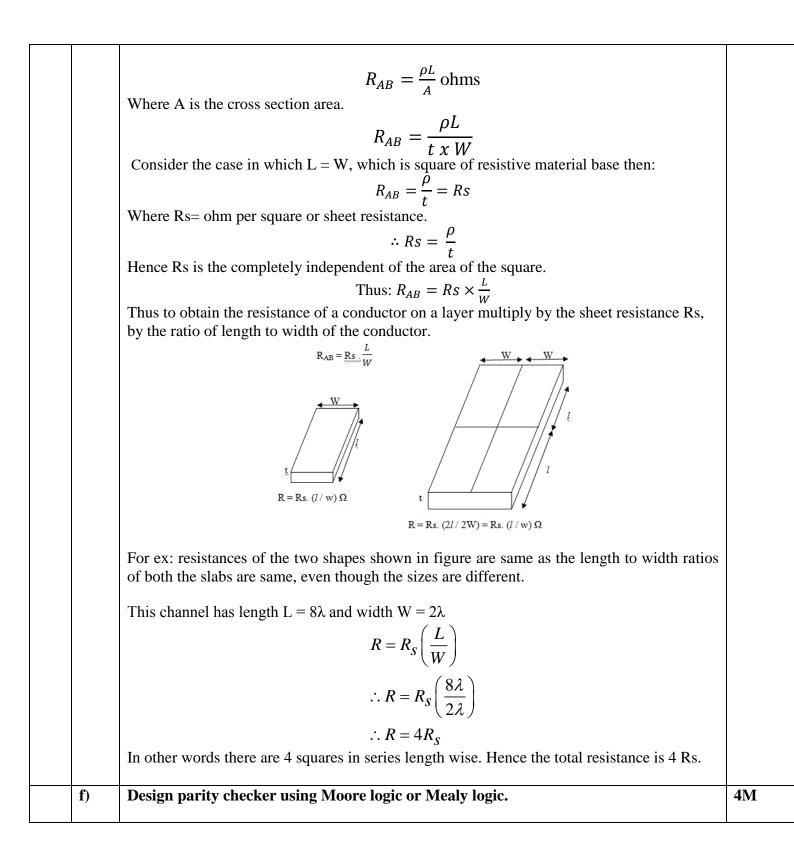

| Ans: | <b><u>Resistance Estimation:</u></b> Consider a uniform slab of conducting material of resistivity $\rho$ . Let W be the width, t the thickness and l is the length of the slab.<br>Hence the resistance between A and B terminal:                                                                                                                                                                                    | 4N         |

|      | Resistivity p                                                                                                                                                                                                                                                                                                                                                                                                         |            |

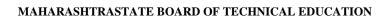

| Ans: | Parity at a lease                                                                 | <b>4</b> M |

|------|-----------------------------------------------------------------------------------|------------|

|      | Parity checker.                                                                   |            |

|      | a) Serial 1/p string                                                              |            |

|      | • Out = 1 if odd of is is input                                                   |            |

|      | · out = 0 if even of is is input                                                  |            |

|      | b) State all a de la company de la                                                |            |

|      | b) Statediagram (Moore madeline)                                                  |            |

|      | 1                                                                                 |            |

|      | or > Even > odd -                                                                 |            |

|      |                                                                                   |            |

|      | 3.                                                                                |            |

|      | as about a state state                                                            |            |

|      | c) state Transistion Mable                                                        |            |

|      | IJP Present state Next state 0/P                                                  |            |

|      | O EVEN BUEN O                                                                     |            |

|      | 1 Even odd o                                                                      |            |

|      | o odd odd !                                                                       |            |

|      | 1 odd even 1                                                                      |            |

|      |                                                                                   |            |

|      | A) che Arcianmenti-                                                               |            |

|      | d) state Assignment:-<br>Evenzo: oddel                                            |            |

|      | Evento; Odde                                                                      |            |

|      | DIP Precent date Next state OF<br>0 0 0 0<br>1 0 1 0<br>1 0 1 1<br>1 1 0<br>1 0 1 |            |

|      |                                                                                   |            |

|      | Skute Excellation toble:-                                                         |            |

|      | CAND CPSIC NSO DHEVE OIL                                                          |            |

|      | 0 0 0 0 0                                                                         |            |

|      | 10110                                                                             |            |

|      | 0 1 1 1                                                                           |            |

|      | 1 1 0 0 1                                                                         |            |

|      | 2)                                                                                |            |

|      | Knap:-                                                                            |            |

|      | (d) Disput (b) OIP                                                                |            |

|      |                                                                                   |            |

|      | $\begin{array}{cccccccccccccccccccccccccccccccccccc$                              |            |

|      | Dins xat xa Y=a                                                                   |            |

|      |                                                                                   |            |

|      |                                                                                   |            |

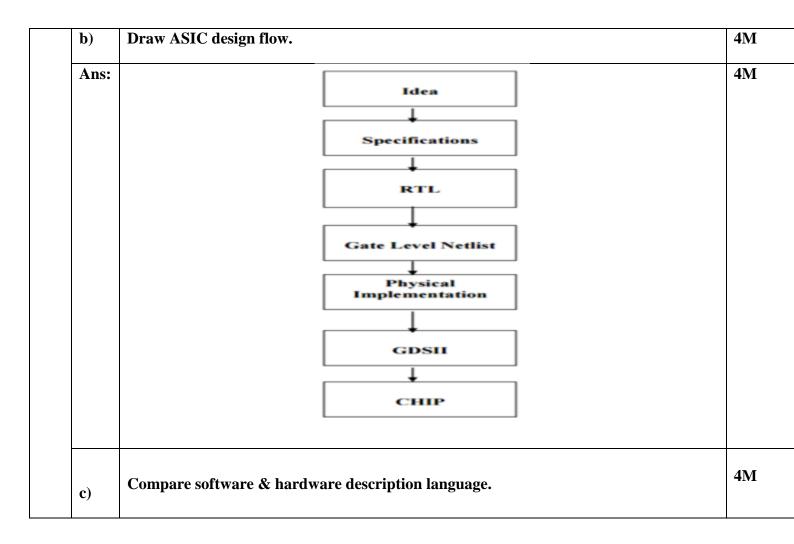

| Q.4 | A)                                                 | Attempt an                                                                                                       | y FOUR :                                                                                                                                                                                                                   | 0 01P                                                                                                                                                                                                                        | 16M        |  |  |

|-----|----------------------------------------------------|------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|--|--|

|     | a)                                                 | Compare F                                                                                                        | PGA and CPLD.                                                                                                                                                                                                              |                                                                                                                                                                                                                              | <b>4</b> M |  |  |

|     | Ans:                                               |                                                                                                                  |                                                                                                                                                                                                                            |                                                                                                                                                                                                                              | <b>4</b> M |  |  |

|     |                                                    | Sr. No                                                                                                           | FPGA                                                                                                                                                                                                                       | CPLD                                                                                                                                                                                                                         |            |  |  |

|     |                                                    | 1.                                                                                                               | It is field programmable gate array.                                                                                                                                                                                       | It is complex programmable logic device.                                                                                                                                                                                     |            |  |  |

|     |                                                    | 2.                                                                                                               | Capacity is defined in terms of number of gates available.                                                                                                                                                                 | Capacity is defined in terms of number of macro cells available.                                                                                                                                                             |            |  |  |

|     |                                                    | 3.                                                                                                               | FPGA consumes less power than CPLD.                                                                                                                                                                                        | CPLD consumes more power than FPGA                                                                                                                                                                                           |            |  |  |

|     |                                                    | 4.                                                                                                               | Number of input and output pins<br>on FPGA are less than CPLD.                                                                                                                                                             | Number of input and output pins on<br>CPLD are more than FPGA.                                                                                                                                                               |            |  |  |

|     |                                                    | 5.                                                                                                               | FPGA is suitable for designs with<br>large number of blocks with few<br>number of inputs.                                                                                                                                  | CPLD is ideal for complex blocks with large number of inputs.                                                                                                                                                                |            |  |  |

|     |                                                    | 6.                                                                                                               | FPGA based designs require more<br>board space and layout is more<br>complex.                                                                                                                                              | CPLD board designs need less board space and layout is less complex.                                                                                                                                                         |            |  |  |

|     |                                                    | 7.                                                                                                               | It is difficult to predict the speed performance of design.                                                                                                                                                                | Speed performance can be easily predicted.                                                                                                                                                                                   |            |  |  |

|     |                                                    | 8.                                                                                                               | FPGA are available in wide density range.                                                                                                                                                                                  | CPLD contain fewer registers but have better performance.                                                                                                                                                                    | 4M         |  |  |

|     | b) Explain cycle based and event based simulators. |                                                                                                                  |                                                                                                                                                                                                                            |                                                                                                                                                                                                                              |            |  |  |

|     | Ans:                                               | 1. Event ba                                                                                                      | sed simulator:                                                                                                                                                                                                             |                                                                                                                                                                                                                              | 2M         |  |  |

|     | All5.                                              | <ul> <li>Event d</li> <li>The sim</li> <li>For this causes simulate</li> <li>Gates w</li> <li>The sim</li> </ul> | riven signal keeps track Of any chang<br>nulator starts simulation as soon as an<br>s the simulator has to keep record of<br>a large memory overload but gives<br>es events only.<br>hose inputs have events are called ac | y signal in event list changes its value.<br>f all the scheduled events in future. This<br>high accuracy for asynchronous design. It<br>etive and are placed in activity list.<br>ate from the activity list. The process Of | 2111       |  |  |