# SUMMER – 2019 EXAMINATION MODEL ANSWER

#### Subject: Advanced Microprocessor

Subject Code:

17627

#### **Important Instructions to examiners:**

- 1) The answers should be examined by key words and not as word-to-word as given in the model answer scheme.

- 2) The model answer and the answer written by candidate may vary but the examiner may try to assess the understanding level of the candidate.

- 3) The language errors such as grammatical, spelling errors should not be given more Importance (Not applicable for subject English and Communication Skills).

- 4) While assessing figures, examiner may give credit for principal components indicated in the figure. The figures drawn by candidate and model answer may vary. The examiner may give credit for any equivalent figure drawn.

- 5) Credits may be given step wise for numerical problems. In some cases, the assumed constant values may vary and there may be some difference in the candidate's answers and model answer.

- 6) In case of some questions credit may be given by judgement on part of examiner of relevant answer based on candidate's understanding.

- 7) For programming language papers, credit may be given to any other program based on equivalent concept.

| Q. | Sub  | Answer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Marking                                              |

|----|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|

| No | Q.N. |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Scheme                                               |

|    | (a)  | Attempt any FIVE:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 20                                                   |

| 1. | Ans  | Explain features of 80386 microprocessor. (any eight)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 4M                                                   |

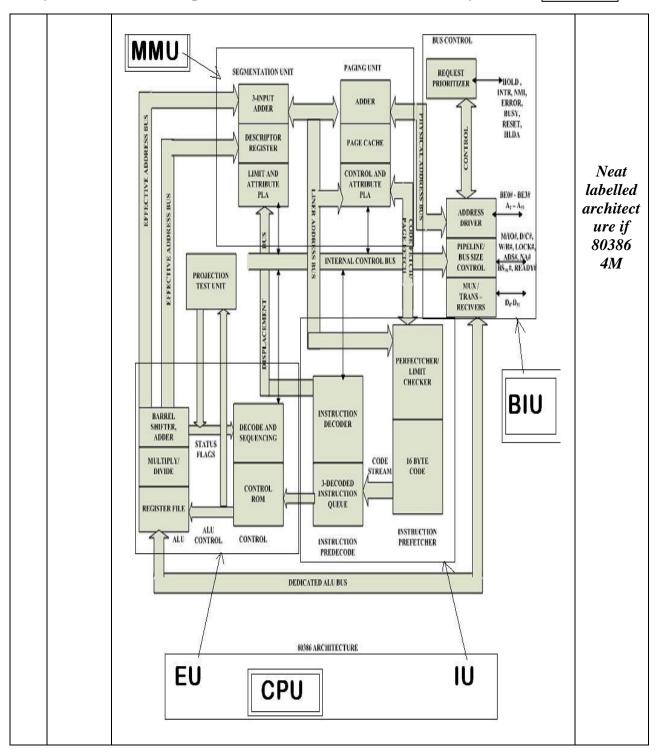

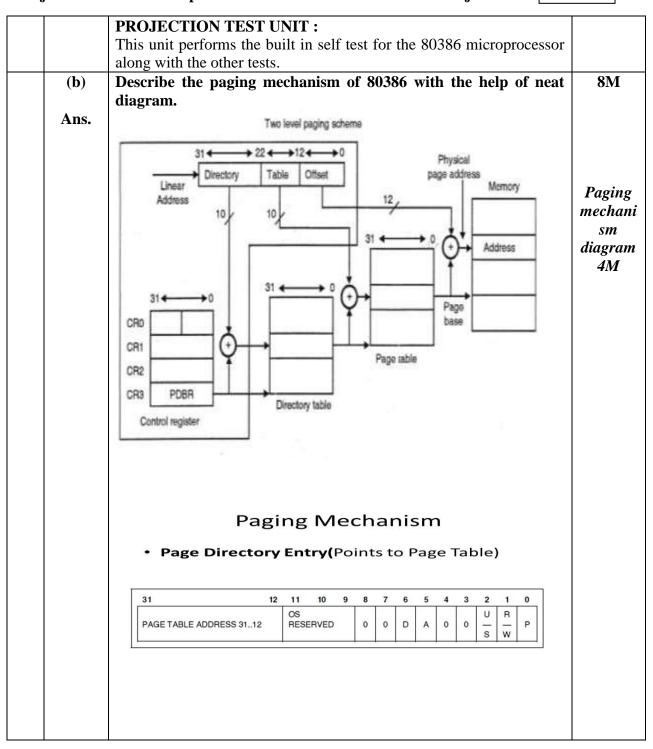

|    | Ans. | <ol> <li>The salient features of 80386 are as follows:</li> <li>It is a 132 PGA (pin grid array) with 32 bits non multiplexed data bus and 32 bits address bus.</li> <li>It works in 3 modes: real, protected and virtual 8086 mode (V-86).</li> <li>It can address total 2<sup>32</sup> i.e., 4GB physical memory with the help of its 32 bits address lines.</li> <li>The integrated memory management unit in 80386 supports segmentation and paging of memory.</li> <li>It supports the interface of 80387-DX coprocessor IC to perform the complex floating point arithmetic operations.</li> <li>It supports 64TB virtual memory.</li> <li>It has an integrated memory management unit which supports the virtual memory and four levels of protections.</li> <li>It has an on chip clock divider circuitry.</li> <li>It has BIST (built in self-test) feature which tests approximately</li> </ol> | Any<br>eight<br>features<br><sup>1/2</sup> M<br>each |

# **SUMMER – 2019 EXAMINATION** MODEL ANSWER

| Subject: Adva | anced Microprocessor Subje                                    | ct Code: 1    | 7627       |

|---------------|---------------------------------------------------------------|---------------|------------|

|               | one half of the 80386 processor when RESET an                 | d BUSY are    |            |

|               | active.                                                       |               |            |

|               | 10. It has breakpoint registers to provide the breakpoint     | traps on code |            |

|               | (instructions) execution or data access.                      | 1             |            |

|               | 11. It supports instruction pipelining with the help          | of 16 bytes   |            |

|               | instruction prefetch queue.                                   |               |            |

|               | 12. It has 8,32 bit General Purpose bits registers to store   | the data and  |            |

|               | address at the time of programming.                           |               |            |

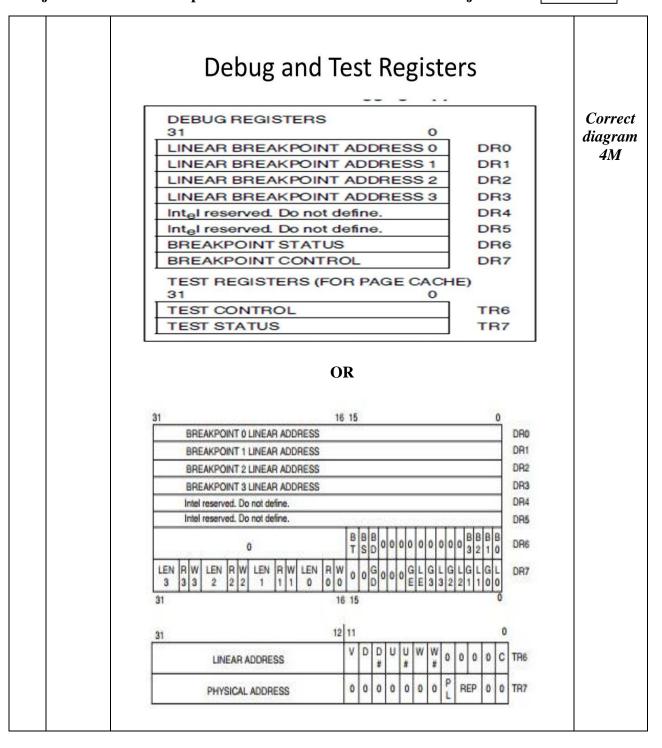

|               | 13. It has 8 debug registers DR0-DR7 for hardware de          | bugging and   |            |

|               | control.                                                      | 00 0          |            |

|               | 14. It has a 32 bit E-flag register.                          |               |            |

|               | 15. It supports the dynamic bus sizing by which the 8         | 0386 can be   |            |

|               | interfaced to 16 bits devices effectively. And also           |               |            |

|               | 8bits, 16 bits and 32 bits operands.                          | 11            |            |

|               | 16. It operates on 20 MHz and 33 MHz frequency.               |               |            |

| (b)           | Draw Register organization format of 80386 DX                 | K. State the  | <b>4</b> M |

|               | function of segment registers.                                |               |            |

| Ans.          | Register organization                                         |               |            |

|               | (General-purpose register, segment register, status and cont  | rol           |            |

|               | register, instruction pointer.                                |               |            |

|               | The 80386 has 32 bits registers which are classified into for | llowing seven |            |

|               | types :                                                       |               |            |

|               | 1. General purpose registers.                                 |               |            |

|               | 2. segment registers                                          |               |            |

|               | 3. instruction pointer and flags registers                    |               |            |

|               | 4. Control registers                                          |               |            |

|               | 5. System address registers                                   |               |            |

|               | 6. debug registers                                            |               |            |

|               | 7. Test registers                                             |               |            |

|               |                                                               |               |            |

|               | General purpose registers                                     |               |            |

|               |                                                               |               |            |

|               |                                                               |               |            |

|               |                                                               |               |            |

|               |                                                               |               |            |

|               |                                                               |               |            |

|               |                                                               |               |            |

|               |                                                               |               |            |

|               |                                                               |               |            |

| Subject: Adv | anced Microprocessor Subject Code: 17                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 627                                                                          |

|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------|

|              | 32 BIT NAMES<br>32 BIT NAMES<br>EAX<br>EAX<br>EAX<br>EBX<br>EAX<br>AH<br>AH<br>AX<br>AH<br>AX<br>AL<br>ACCUMULATOR<br>BASE INDEX<br>CH<br>CX<br>CH<br>CX<br>CH<br>CX<br>CH<br>CX<br>CL<br>COUNT<br>DATA<br>SP<br>STACK POINTER<br>EBP<br>EDI<br>DI<br>DI<br>DI<br>DI<br>DI<br>DI<br>DI<br>SU<br>SURCE INDEX                                                                                                                                                                                                                                                                                | Diagram<br>of<br>register<br>organiza<br>tion<br>format<br>of 80386<br>DX 2M |

|              | eip ip<br>eflags flags                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                              |

|              | Segment registers:<br>There are total 6 segment registers of 16 bits each in 386. They are<br>corresponding to CS, DS, ES, SS,FS, GS.<br>In real mode size of each segment is 64kB while in protected mode<br>each segment could be of 4GB.<br>The CS and SS are used as code and stack segment respectively while<br>the DS, FS, GS, ES are used as the data segments in 386.<br>The segment registers in protected mode are called as segment<br>selectors.<br>These registers CSR, SSR, DSR, ESR, FSR and GSR are used in the<br>relational address calculation in the different modes. | Functio<br>n of<br>segment<br>registers<br>2M                                |

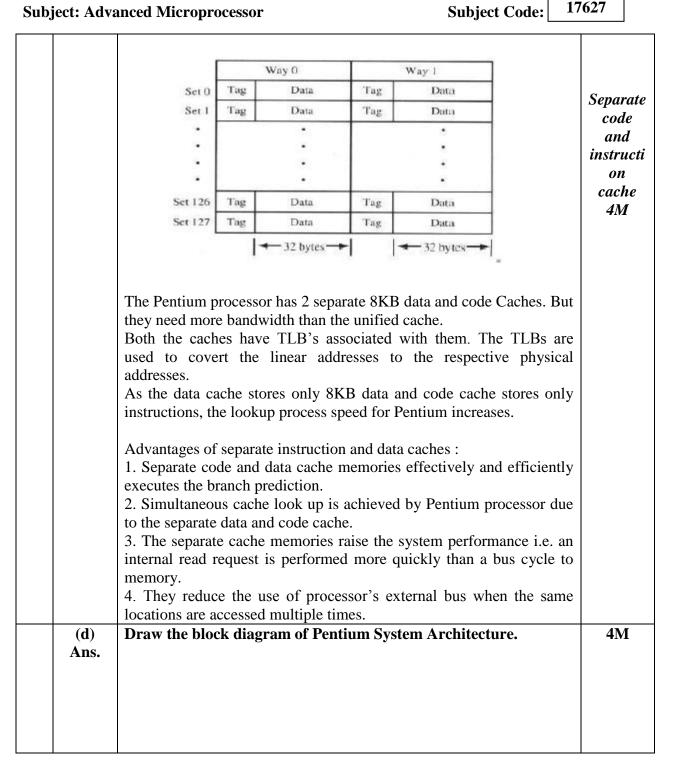

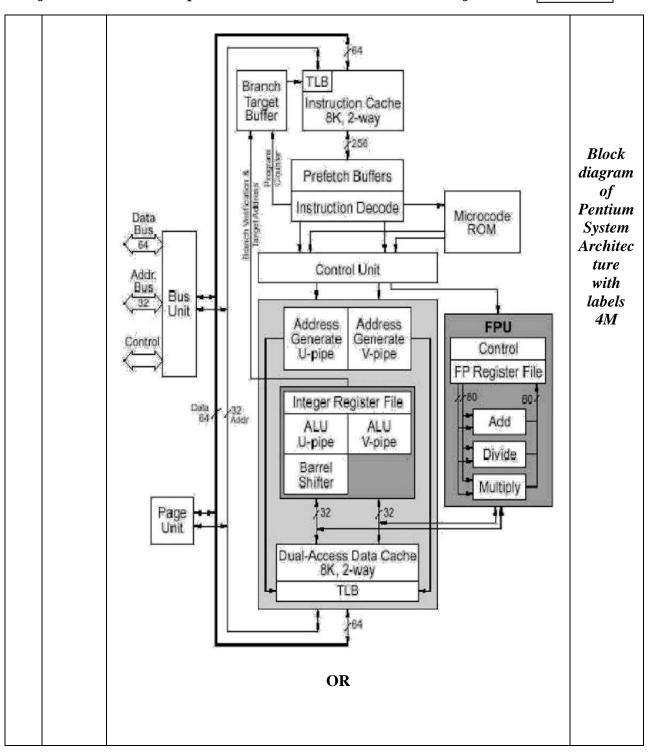

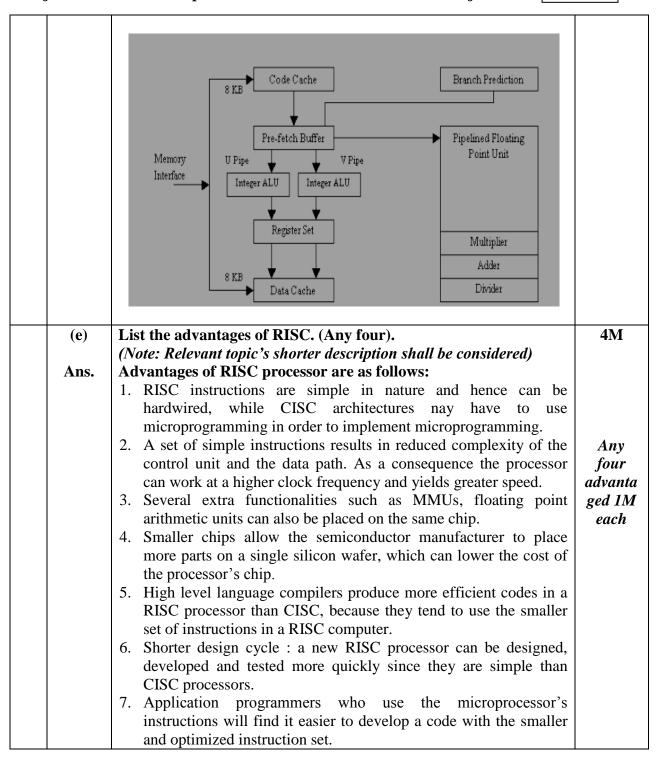

| (c)<br>Ans.  | <ul> <li>physical address calculation in the different ways in different modes in 80386.</li> <li>Justify the use of separate cache in Pentium configuration.</li> <li>Separate 8K B instruction and Data Cache :<br/>The following figure shows the organization of instruction and data cache.</li> </ul>                                                                                                                                                                                                                                                                                | 4M                                                                           |

# **SUMMER – 2019 EXAMINATION MODEL ANSWER**

#### **Subject: Advanced Microprocessor**

# SUMMER – 2019 EXAMINATION MODEL ANSWER

**Subject: Advanced Microprocessor**

Subject Code: 17627

# SUMMER – 2019 EXAMINATION MODEL ANSWER

Subject: Advanced Microprocessor

Subject Code: 17627

| Subject: Adva | nced Microprocessor                                                                                                                                                                                                                                                                                                                                                                                                                                                | Subject Code:                                                   | 17627                                                |                         |

|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------|------------------------------------------------------|-------------------------|

|               | 8. The loading and decoding of the instructions<br>is simple and fast and it is not needed to wa<br>the instruction is known in order to start dec<br>one. Decoding is simplified as op-code an<br>located in the same location for all instruction                                                                                                                                                                                                                | it until the length<br>coding the followind<br>address fields a | of<br>ng                                             |                         |

| ( <b>f</b> )  | Describe any four DOS interrupts.                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                 | 4N                                                   | 1                       |

| Ans.          | <ul> <li>INT21</li> <li>1) 3CH : to create file</li> <li>Registers to be used before calling the function of CX=File Attribute DS: DX - full file path (zero for ASCIIZ String file descriptor;</li> <li>a start variable in data segment loaded to DX</li> <li>Syntax: mov ah, 3Ch; function 3Ch - create a file int 21h; transfer to DOS</li> </ul>                                                                                                              | terminated) – an                                                |                                                      |                         |

|               | <ul> <li>2) 3DH: to open file</li> <li>This function opens the indicated file</li> <li>Registers to be used before calling the function of DS: DX - an ASCIIZ String file descriptor</li> <li>AL=Access Code and sharing modes are as follo</li> <li>00H- Open for reading mode</li> <li>01H- open for writing mode</li> <li>02H – open for read/write mode</li> <li>Syntax: mov ah,3Dh; function 3Dh - open the file</li> <li>int 21h; transfer to DOS</li> </ul> | DWS                                                             | Desc.<br>ion<br>any f<br>DO<br>interr<br>s 11<br>eac | of<br>Sour<br>Sour<br>M |

|               | 3) <b>3EH: to close the file</b><br>This function closes the indicated file<br>Registers to be used before calling the function of<br>BX = file handle<br><i>Syntax</i> : mov ah, 3Eh; function 3Eh - close a file<br>int 21h; transfer to DOS                                                                                                                                                                                                                     | -                                                               |                                                      |                         |

|               | <ul> <li>4) 3FH: to read the file</li> <li>This function reads up to CX bytes from the Ind the specified memory buffer. On successful return contains the number of bytes actually read.</li> <li>Registers to be used before calling the function of BX = file handle</li> </ul>                                                                                                                                                                                  | rn, the AX Registe                                              | r                                                    |                         |

| Subject: Ad | Ivanced Microprocessor Subject Code: 17627                               |

|-------------|--------------------------------------------------------------------------|

|             | CX = number of bytes to read                                             |

|             | DS:DX -> buffer for data                                                 |

|             | Syntax: mov ah,3Fh; function 3Fh – read the file                         |

|             | int 21h; transfer to DOS                                                 |

|             |                                                                          |

|             | 5) 40H: to write to the file                                             |

|             | This function writes the specified number of bytes from a buffer         |

|             | to a file or device.                                                     |

|             | Registers to be used before calling the function using INT 21H:          |

|             | BX = file handle                                                         |

|             | CX = number of bytes to write                                            |

|             | DS:DX -> data to write                                                   |

|             | Syntax: mov ah,40h; function 40h - write to file                         |

|             | int 21h; transfer to DOS                                                 |

|             | 6) 41H: to delete the file                                               |

|             | This function deletes the specified file                                 |

|             | Registers to be used before calling the function using INT 21H:          |

|             | ASCIIZ filename DS: DX - zero terminated full paths.                     |

|             | Syntax: mov ah, 41h; delete file int 21h; transfer to DOS                |

|             | 7) 56H: to rename the file                                               |

|             | This functions renames the given file with new name specified by         |

|             | ES: DI                                                                   |

|             | Registers to be used before calling the function using INT 21H :         |

|             | DS: DX address of ASCIIZ filename of existing file ES : DI –             |

|             | ASCIZ new filename                                                       |

|             | Syntax: mov ah, 56h; delete file int 21h; transfer to DOS                |

|             |                                                                          |

|             | 8) 43H: Set/Get file attribute                                           |

|             | This function gets or sets the file attributes                           |

|             | Registers to be used before calling the function using INT 21H:          |

|             | AL = 00H to get attributes 01H to set attributes $CX = file attributes,$ |

|             | if AL=01H. Bits can be combined DS: $DX =$ segment: offset of            |

|             | ASCIIZ pathname                                                          |

|             | Syntax: mov ah, 43h; set/get file attributes int 21h; transfer to DOS    |

|             | 9) 57H: Set/Get file time & date                                         |

|             | This function gets or sets the file date and time.                       |

|             | Registers to be used before calling the function using INT 21H:          |

Subject: Advanced Microprocessor

## MAHARASHTRA STATE BOARD OF TECHNICAL EDUCATION (Autonomous) (ISO/IEC - 27001 - 2005 Certified)

# SUMMER – 2019 EXAMINATION MODEL ANSWER

Subject Code: 17627

| -    |                                                                           |

|------|---------------------------------------------------------------------------|

|      | AL = 00h  or  01H (0 - get  1 - set)                                      |

|      | BX = file handle                                                          |

|      | DS: DX = segment: offset of ASCIIZ pathname                               |

|      | Syntax: mov ah, 57h; set/get file date and time int 21h; transfer to      |

|      | DOS                                                                       |

|      |                                                                           |

|      | INT 26H                                                                   |

|      | INT26H Absolute Disk Write                                                |

|      | On entry:                                                                 |

|      | AL Drive number (0=A, 1=B)                                                |

|      | CX Number of sectors to write                                             |

|      |                                                                           |

|      | DX Starting sector number                                                 |

|      | DS:DX Address of sectors to write                                         |

|      |                                                                           |

|      | <b>Returns:</b> AX Error code (if CF is set; see below)                   |

|      | Flags DOS leaves the flags on the stack                                   |

|      | This interrupt reads one or more sectors from a disk drive, and is        |

|      | comparable to the service provided by the ROM BIOS in Interrupt           |

|      | 13h.                                                                      |

|      | INT 25h Absolute Disk Read                                                |

|      | eads one or more sectors on a specified logical disk.                     |

|      |                                                                           |

|      | On entry:                                                                 |

|      | AL Drive number (0=A, 1=B)                                                |

|      | CX Number of sectors to read                                              |

|      | DX Starting sector number                                                 |

|      | DS:DX Buffer to store sector read                                         |

|      |                                                                           |

|      | <b>Returns:</b> AX Error code (if CF is set; see below)                   |

|      | Flags DOS leaves the flags on the stack                                   |

| (g)  | Differentiate between hardware and software interrupts. (4 4M             |

|      | points).                                                                  |

| Ans. | Sr.         Hardware interrupts         Software interrupts         Any   |

|      | No.                                                                       |

|      | 1It is an unsynchronous eventIt is synchronous event <i>points</i>        |

|      | 2 It is requested by external It is requested by executing <i>1M each</i> |

|      | device or pin.                                                            |

|      |                                                                           |

2.

**(a)** Ans.

#### MAHARASHTRA STATE BOARD OF TECHNICAL EDUCATION (Autonomous) (ISO/IEC - 27001 - 2005 Certified)

# **SUMMER – 2019 EXAMINATION**

# Subject: Adva

DOS

BIOS

Hardware/ Devices

| MODEL ANSWER |                                                                        |                                                                                                                                             |                                                                                                                                                                                                                          |                                |  |

|--------------|------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------|--|

| 11           | nced M                                                                 | licroprocessor                                                                                                                              | Subject Code: 17                                                                                                                                                                                                         | 627                            |  |

|              | 3                                                                      | Program counter is not incremented                                                                                                          | Program counter is incremented                                                                                                                                                                                           |                                |  |

|              | 4                                                                      | The micro processor<br>executes 2 acknowledgement<br>cycles on the receipt of<br>software interrupt                                         | The micro processor does<br>not execute any<br>acknowledgement cycle on<br>the receipt of software<br>interrupt                                                                                                          |                                |  |

|              | 5                                                                      | It can be ignored or masked except for TRAP.                                                                                                | It cannot be ignored or masked                                                                                                                                                                                           |                                |  |

|              | 6                                                                      | It has comparatively lower priority                                                                                                         | It has highest priority among<br>all the interrupts                                                                                                                                                                      |                                |  |

|              | Explai<br>DOS I<br>Figure<br>routine<br>initiali<br>reading<br>interfa | es in a ROM to provide the devices<br>zes attached devices and provide<br>g to and writing from the device<br>with BIOS when there is a new | OS interface.<br>Face. BIOS contains a set of<br>ce supports. The BIOS tests and<br>ride services that are used for<br>vices. One task of DOS is to<br>red to access its facilities. When<br>of DOS, it may transfer the | 16<br>4M<br>Explana<br>tion 2M |  |

|              | reques<br>Someti                                                       | t to BIOS which in turn accesses                                                                                                            | s the requested device.<br>request to BIOS, especially for                                                                                                                                                               |                                |  |

|              |                                                                        | User programs                                                                                                                               |                                                                                                                                                                                                                          | Diagram<br>2M                  |  |

| Subject: Adv | anced Microprocessor Subject Code:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 17627                                                 |                 |

|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------|-----------------|

| (b)<br>Ans.  | <ul> <li>State and explain features of RISC processors. (Any four)</li> <li>Features of RISC processors: <ol> <li>Simple instruction set: in a RISC machine, the instruction is contains simple basic instructions, from which more compliinstructions can be composed. These instructions with less latency a preferred.</li> <li>Same length instructions: each instruction is of same length, that it may be fetched in a single operation. The tradition microprocessors from intel or Motorola support variable leng instructions.</li> <li>Single machine cycle instruction: Most instructions complete one machine cycle, which allows the processor to handle seve instruction), which is due to optimization of each instruction the CPU and massive pipelining embedded in a RISC processor.</li> <li>Pipelining: usually massive pipelining is embedded in a RIS processor, The pipelining is key to speed up RISC machines.</li> <li>Very few addressing modes and formats: unlike the CIS processors, where the number of addressing modes are very high. RISC processors the addressing modes are much less and it suppofew formats.</li> <li>Large number of registers: the RISC design philosophy genera incorporates a larger number of registers to prevent in large amound of interactions with memory.</li> <li>Micro-coding is not required: Unlike in CISC machines, in RIS architecture, instruction micro-coding is not required. This is becaut of the availability of a set of simple instructions and simplinistructions and simplications may be easily built into the hardware.</li> </ol> </li> </ul> | lex are so An four four four four four four four four | y<br>ur<br>vres |

| (c)<br>Ans.  | Describe the floating point unit operation in Pentium processor.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | . 4N                                                  | 1               |

# SUMMER – 2019 EXAMINATION MODEL ANSWER

Subject: Advanced Microprocessor

Subject Code: 17627

# **SUMMER – 2019 EXAMINATION** MODEL ANSWER

| Subje | ect: Adva   | nced Microprocessor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Subject Code:                           | 17627 | ] |

|-------|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|-------|---|

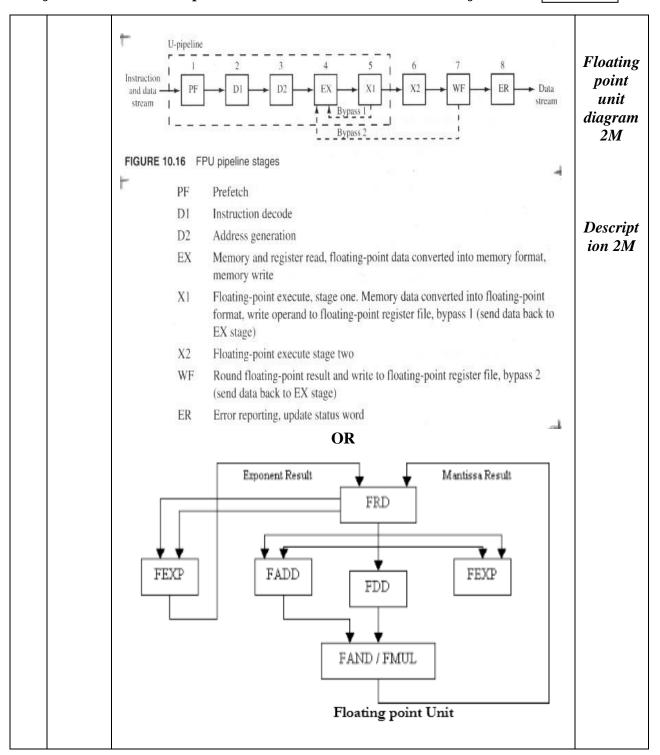

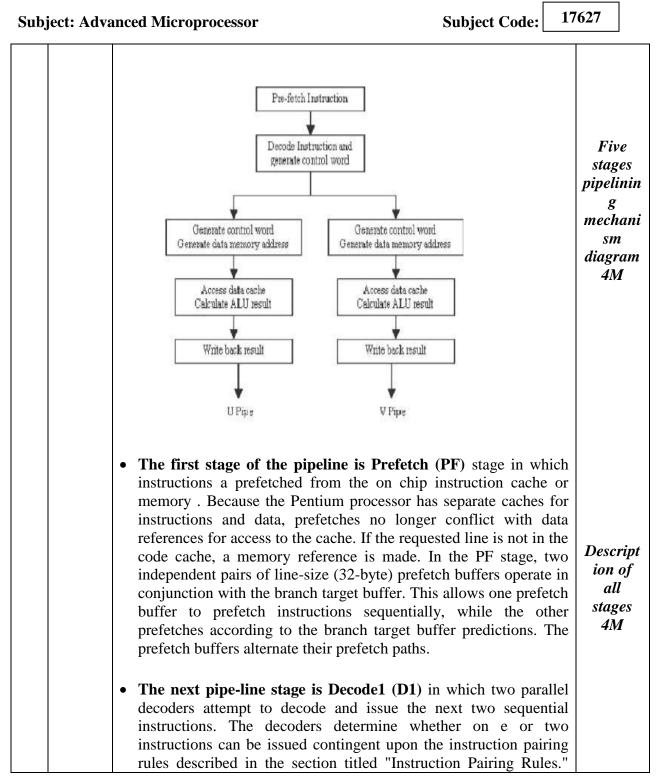

|       |             | <ul> <li>Floating Point Pipeline : Floating Point Unit<br/>Processor : The floating point pipeline has 8 stages a</li> <li>1. Prefetch (PF) :</li> <li>Instructions are prefetched from the on-chip instruction</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | as follows:                             | ium   |   |

|       |             | <ul> <li>2. Instruction Decode (D1):</li> <li>Two parallel decoders attempt to decode and sequential instructions</li> <li>It decodes the instruction to generate a control word</li> <li>A single control word causes direct execution of a</li> <li>Complex instructions require micro-coded control</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | issue the next<br>ord<br>an instruction | two   |   |

|       |             | <ul> <li>3. Address Generate (D2):</li> <li>Decodes the control word</li> <li>Address of memory resident operands are calculated and the control word and th</li></ul> | ted                                     |       |   |

|       |             | <ul> <li>4. Memory and Register Read (Execution Stage)</li> <li>Register read, memory read or memory write per by the instruction to access an operand.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                         | ired  |   |

|       |             | <ul> <li>5. Floating Point Execution Stage 1 (X1):</li> <li>Information from register or memory is written in</li> <li>Data is converted to floating point format before floating point unit.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | -                                       | o the |   |

|       |             | <ul><li>6. Floating Point Execution Stage 2 (X2):</li><li>Floating point operation performed within floating</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | g point unit.                           |       |   |

|       |             | <ul> <li>7. Write FP Result (WF):</li> <li>Floating point results are rounded and the result target floating point register.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | ult is written to                       | the   |   |

|       |             | <ul> <li>8. Error Reporting(ER)</li> <li>If an error is detected, an error reporting stage error is reported and</li> <li>FPU status word is updated.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | is entered where                        | the   |   |

|       | (d)<br>Ans. | Explain features of Intel MMX Architecture.<br>Features of Intel MMX Architecture:<br>1. 57 new microprocessor instructions have been a<br>designed to handle video, audio, and graphical dat                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                         | 4N    | 1 |

| Subject: Adva | anced I                                                                   | Microprocessor                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Subject Code: 1'                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 7627                               |

|---------------|---------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------|

|               | to a n<br>2. Ne<br>3. A t<br>possil<br>multij<br>4. The<br>mean<br>5. 8,6 | • • • •                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | isible state.<br>dword).(4 new MMX data types)<br>Multiple Data (SIMD), makes it<br>n the same operation on<br>ocessor has increased to 32 KB,<br>nat is off the microprocessor.                                                                                                                                                                                                                                                                                                 | Any<br>four<br>features<br>1M each |

| (e)           | Com                                                                       | pare between GDTR and LDT                                                                                                                                                                                                                                                                                                                                                                                                                                                   | <b>'R.</b> (four points)                                                                                                                                                                                                                                                                                                                                                                                                                                                         | <b>4M</b>                          |

| Ans.          | Sr.<br>No                                                                 | GDTR<br>(Global Descriptor Table<br>Register )                                                                                                                                                                                                                                                                                                                                                                                                                              | LDTR<br>(Local Descriptor Table<br>Register)                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                    |

|               |                                                                           | The Global Descriptor Table<br>Register (GDTR) is a<br>dedicated 48-bit (6 byte)<br>register used to record the<br>base and size of a system's<br>global descriptor table<br>(GDT). Thus, two of these<br>bytes define the size of the<br>GDT, and four bytes define<br>its base address in physical<br>memory. LIMIT is the size<br>of the GDT, and BASE is the<br>starting address. LIMIT is 1<br>less than the length of the<br>table, then the GDT is 16<br>bytes long. | The Local Descriptor Table<br>Register (LDTR) is a<br>dedicated 48-bit register that<br>contains, at<br>any given moment, the base<br>and size of the local<br>descriptor table (LDT)<br>associated with the<br>Currently executing task.<br>Unlike GDTR, the LDTR<br>register contains both a<br>"visible" and a<br>"hidden" component. Only<br>the visible component is<br>accessible, while the hidden<br>component remains truly<br>inaccessible to application<br>programs. | Any<br>four<br>points<br>IM each   |

|               |                                                                           | There is no visible<br>component of GDTR.<br>To load the GDTR, LGDT                                                                                                                                                                                                                                                                                                                                                                                                         | The visible component of<br>the LDTR is a 16-bit<br>"selector"<br>The dedicated, protected                                                                                                                                                                                                                                                                                                                                                                                       |                                    |

|               |                                                                           | instruction is used.                                                                                                                                                                                                                                                                                                                                                                                                                                                        | instructions LLDT and<br>SLDT are reserved for<br>loading and storing,                                                                                                                                                                                                                                                                                                                                                                                                           |                                    |

| Subject: Adva | Subject: Advanced Microprocessor Subject Code: 170                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                    |

|---------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|

|               | Structure of GDTR :           47         BASE(32 bit)         16         15         LIMIT         0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | respectively, the visible<br>selector component of the<br>LDTR register.<br>Structure of LDTR :<br>$\begin{array}{c c} & & & \\ \hline \hline & & \\ \hline & & \\ \hline & & \\ \hline & & \\ \hline \hline & & \\ \hline & & \\ \hline \hline & & \\ \hline \hline \\ \hline & & \\ \hline \hline & & \\ \hline \hline \\ \hline & & \\ \hline \hline \\ \hline & & \\ \hline \hline \\ \hline \hline & & \\ \hline \hline \hline \\ \hline \hline \\ \hline \hline \\ \hline \hline \hline \\ \hline \hline \hline \hline$ |                    |