(Autonomous) (ISO/IEC - 27001 - 2005 Certified)

#### WINTER- 16 EXAMINATION (Subject Code: 17321) Model Answer

#### **Important Instructions to examiners:**

- The answers should be examined by key words and not as word-to-word as given in themodel answer scheme.

- 2) The model answer and the answer written by candidate may vary but the examiner may tryto assess the understanding level of the candidate.

- 3) The language errors such as grammatical, spelling errors should not be given moreImportance (Not applicable for subject English and Communication Skills.

- 4) While assessing figures, examiner may give credit for principal components indicated in the figure. The figures drawn by candidate and model answer may vary. The examiner may give credit for any equivalent figure drawn.

- 5) Credits may be given step wise for numerical problems. In some cases, the assumed constantvalues may vary and there may be some difference in the candidate's answers and model answer.

- 6) In case of some questions credit may be given by judgement on part of examiner of relevant answer based on candidate's understanding.

- 7) For programming language papers, credit may be given to any other program based on equivalent concept.

| Q.<br>No. | Sub<br>Q.N. | Answer                                                                                                                                                                      | Marking<br>Scheme |

|-----------|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|

| Q.1       |             | Attempt any SIX of following                                                                                                                                                | 12-Total<br>Marks |

| 1         | A)          | Draw symbol of P-N diode, Zener diode.                                                                                                                                      | 2 M               |

|           | Ans:        | P-N diode                                                                                                                                                                   | 1M                |

|           |             | A—K                                                                                                                                                                         |                   |

|           |             | Zener diode                                                                                                                                                                 | 1M                |

|           |             | A——K                                                                                                                                                                        |                   |

|           | (b)         | Define the term rectification efficiency and rectifier.                                                                                                                     | 2 M               |

|           | Ans:        | Rectification efficiency ( $\eta$ )-It is defined as the ratio of DC output power to the input power from the AC supply $\eta = \frac{DC\ Output\ Power}{AC\ input\ Power}$ | 1M                |

|           |             | <b>Rectifier-</b> It is an electronic circuit which is used to convert AC into pulsating DC. Rectifier is the initial state of regulated power supply.                      | 1M                |

|           |             |                                                                                                                                                                             |                   |

|           | (c)         | List the types of Biasing in BJT.                                                                                                                                           | 2 M               |

|           | Ans:        | Types of Biasing Circuits: i) Base bias (Fixed bias)                                                                                                                        |                   |

| Ans:       | NAND Gate                                                                                             | - out                                                                                                                          | 1M                |

|------------|-------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------|-------------------|

|            |                                                                                                       |                                                                                                                                |                   |

|            | NOR Gate                                                                                              |                                                                                                                                |                   |

|            | A<br>B                                                                                                | out                                                                                                                            | 1M                |

| (h)        | Convert : i) $(456)_D = ()_B$ ii) $(5$                                                                | $(\mathbf{A})_{\mathbf{H}} = (\ )_{\mathbf{D}}$                                                                                | 2 M               |

| Ans:       | i)(456)D=(111001000)B                                                                                 |                                                                                                                                | 1M                |

|            | ii)(5A)H = ( )D<br>= 5 x 161 + 10 x 160<br>= 80 + 10                                                  |                                                                                                                                | 43.5              |

| <b>B</b> ) | = (90)D<br>Attempt any <u>TWO</u> of following                                                        | a.                                                                                                                             | 1M<br>8 M         |

| <b>D</b> ) |                                                                                                       |                                                                                                                                | O IVI             |

| (a)        | Compare intrinsic and extrins                                                                         | sic semiconductor (any 4 points).                                                                                              | 4 M               |

| Ans:       | Intrinsic Semiconductor These are pure semiconducting materials and no impurity atoms are added to it | Extrinsic Semiconductor  When some impurity is added in the intrinsic semiconductor, extrinsic semiconductors can be produced. | 1 M for each poir |

|            | The electrical conductivity is low.                                                                   | The electrical conductivity is high.                                                                                           |                   |

|            | The electrical conductivity of intrinsic semiconductors depends on their temperatures.                | The electrical conductivity depends on the amount of impurity added in them.                                                   |                   |

|            | e.g The crystals of pure elements like germanium and silicon                                          | e.g. P & N type semiconductor                                                                                                  |                   |

| <b>(b)</b> | Explain full wave bridged rect output waveform.                                                       | ifier with the help of circuit diagram and input                                                                               | 4 M               |

| Ans:       | vin 000000                                                                                            | D <sub>3</sub> D <sub>1</sub> + D <sub>2</sub> R <sub>L</sub> -                                                                | 2M                |

|            | Operation:                                                                                            | =                                                                                                                              |                   |

(Autonomous) (ISO/IEC - 27001 - 2005 Certified)

#### 1. In positive half cycle (0 to $\Pi$ ):

The end A of the secondary winding becomes positive and end B negative.

This makes diode D1 and D4 forward biased while diode D2 and D3 are reverse biased.

These two diodes will be in series through the load RL. The conventional current direction is as follows.

$$A - D1 - RL - D4 - B$$

**1M**

This makes load voltage polarities as shown in the fig above.

#### 2. In negative half cycle ( $\Pi$ to $2\Pi$ ).

The end B is positive and A is negative. This makes diode D2 and D3 forward biased and diode D1 and D4 is reverse biased.

The conventional current through diode D2 and D3 when it is conducting is as follows.

$$B-D2-RL-D3-A$$

1M

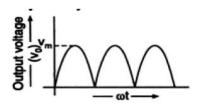

## (c) Explain working of n-p-n transistor in unbiased condition.

#### 4 M 2M

#### **Ans:** Construction of NPN transistor:

**Z**IVI

For an unbiased transistor no external power supplies are connected to it. Base is sandwiched between collector & emitter terminal. It is thin & lightly doped layer.

Emitter & collector layers are wider than base & heavily doped than base.

A transistor is formed of two P-N junctions. For unbiased P-N junctions, the depletion regions are formed. The fig(a) shows the depletion regions formed at the B-E and C-B junctions of n-p-n transistor.

Due to this depletion region any kind of current will not flow due to majority carrier but very small amount of current will flow because of thermally generated minority carrier.

To break this depletion layer there is a need of providing external power supply to transistor & this process is known as Biasing.

2M

|            | Attempt any f                                                             | Cour of following               | :                  |                                                                   | 16         |

|------------|---------------------------------------------------------------------------|---------------------------------|--------------------|-------------------------------------------------------------------|------------|

| a)         | List specificat                                                           | ion of zener diod               | le (any 4).        |                                                                   | 4M         |

| Ans:       | 1. Zener Volta 2. Maximum Z 3. Power dissip 4. Operating te 5. Dynamic Re | Zener current pation emperature |                    |                                                                   | 1M each    |

| <b>b</b> ) | Compare hal                                                               | f wave rectifier,               |                    | tapped rectifier and full wave bridge<br>) TUF 4) Output waveform | 4M         |

| Ans:       | Parameters                                                                | HWR                             | FWCTR              | FWBR                                                              | 1M each fo |

|            | Ripple factor                                                             | 1.21                            | 0.482              | 0.482                                                             | points     |

|            | Rectificatio<br>n efficiency                                              | 40.6%                           | 81.2%              | 81.2%                                                             |            |

|            | TUF<br>Waveforms                                                          | 0.282                           | 0.693              | 0.812                                                             |            |

| <b>c</b> ) | Explain R-C                                                               | (b) Output Voltage (V.)         | r with circuit dia | agram.                                                            | 4M         |

| Ans:       |                                                                           |                                 | + <u>V</u> c       | <u>c</u>                                                          | Diagram:2  |

(Autonomous) (ISO/IEC - 27001 - 2005 Certified)

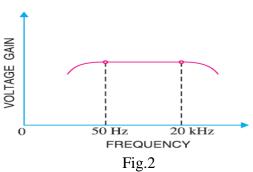

Frequency response curve: The curve representing the variation of gain of an amplifier with frequency is known as frequency response curve. It is shown in Fig. 2. The voltage gain of the amplifier increases with the frequency, f and attains a maximum value. The maximum value of the gain remains constant over a certain frequency range and afterwards the gain starts decreasing with the increase of the frequency. It may be seen to be divided into three regions.

- 1) Low frequency range (20 kHz).

- 2) Mid frequency range (50 Hz to 20 KHz) and

- 3) High frequency range (> 20 kHz)

#### d) Explain construction of n-channel JFET with neat sketch.

**4M**

#### Ans:

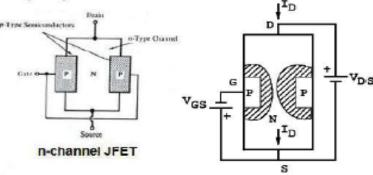

#### N-channel JFE1 (FE1):

Diagram:2 M & Explanatio n:2M

#### Construction:

The n-channel JFET has n-type semiconductor used as a channel which has two terminals, drain and source. Two p-type semiconductors are attached at both sides of n-channel and forms third terminal gate. Thus pn junction exists between gate

#### and source.

- When V<sub>GS</sub> = 0 volt:

- When a voltage is applied between the drain and source with a DC supply voltage  $V_{DD}$  with  $V_{GS}=0$  V, the electrons flow from source to drain through the narrow channel existing between the depletion regions. This constitutes drain current  $I_D$ . The value of drain current is maximum when  $V_{GS}=0$  V. This current is designated vy the symbol  $I_{DSS}$ .

- When V<sub>GS</sub> is negative:

When V<sub>GS</sub> is increased below zero i.e negative, the reverse voltage across the gate source junction is incrased. As a result depletion regions are widened. This reduces effective width of channe and therefore controls the flow of drain current through the channel.

If V<sub>GS</sub> is increased further, two depletion regions touch each other. The drain current reduces to zero. The gate to source voltage at which current reduces to zero is called as pinch-off voltage.

| e)   | Compare CE, CB, CC v impedance 4) Output impedance.                  | v.r.t. to 1) Current            | t gain 2)Voltage                | e gain 3) Input                        | 4M      |

|------|----------------------------------------------------------------------|---------------------------------|---------------------------------|----------------------------------------|---------|

| Ans: | Comparison betwee                                                    | n CB, CE and CC co              | onfigurations:                  |                                        | 1M each |

|      | Parameter                                                            | СВ                              | CE                              | CC                                     | point   |

|      | Input Impedance                                                      | Low                             | Medium                          | High                                   | Pome    |

|      | 1                                                                    | Or                              | Or                              | Or                                     |         |

|      |                                                                      | 50Ω                             | 600Ω to $4kΩ$                   | 1 ΜΩ                                   |         |

|      | Current Gain                                                         | Less than or equal              | High                            | High                                   |         |

|      |                                                                      | to 1                            | Or                              | Or                                     |         |

|      |                                                                      | Or                              | $I_c$                           | $I_{\mathbb{P}}$                       |         |

|      |                                                                      | I <sub>c</sub>                  | $\beta = \frac{c}{I}$           | $\gamma = \frac{L}{I}$                 |         |

|      |                                                                      | $\alpha = \frac{c}{I}$          | 1 <sub>B</sub>                  | 18                                     |         |

|      | Voltage Gain                                                         | Medium                          | Medium                          | Less than or equal                     |         |

|      | Voltage Gam                                                          | Mcdidiii                        | McGiuii                         | to 1                                   |         |

|      | Output Impedance                                                     | High                            | Medium                          | Low                                    |         |

|      | Output Impedance                                                     | Or                              | Or                              | Or                                     |         |

|      |                                                                      | 50 kΩ                           | 10 kΩ to 50 kΩ                  | 50Ω                                    |         |

|      |                                                                      |                                 |                                 |                                        |         |

| f)   | Explain with circuit dia                                             | ngram operation o               | f zener diode as v              | voltage regulator.                     | 4M      |

| Ans: |                                                                      |                                 |                                 |                                        | Diagram |

|      | Current limiting resistor                                            |                                 | Reverse V <sub>z</sub>          | † <sub>a</sub>                         | M &     |

|      | +9                                                                   |                                 | voltage                         |                                        | Explana |

|      | R <sub>s</sub>                                                       | I <sub>z</sub> I <sub>l</sub> T |                                 | I <sub>o</sub>                         | n :2M   |

|      |                                                                      | 2                               | T 1                             | I <sub>z min.</sub>                    |         |

|      | Unregulated                                                          | . }                             | _     \                         | - Knee                                 |         |

|      | DC 7                                                                 |                                 | Zener<br>region                 |                                        |         |

|      | voltage (V <sub>in</sub> )                                           | 7 > 1.                          | 1                               |                                        |         |

|      | 1                                                                    | ,                               | 11                              |                                        |         |

|      | ↓                                                                    |                                 | <b>Y</b>                        | ······································ |         |

|      | -0                                                                   |                                 |                                 | ◆ Reverse current                      |         |

|      | (a) Regulator circuit u                                              | si <mark>ng</mark> Zener Diode  | (b) Reverse c                   | haracteristics of Zener Diode          |         |

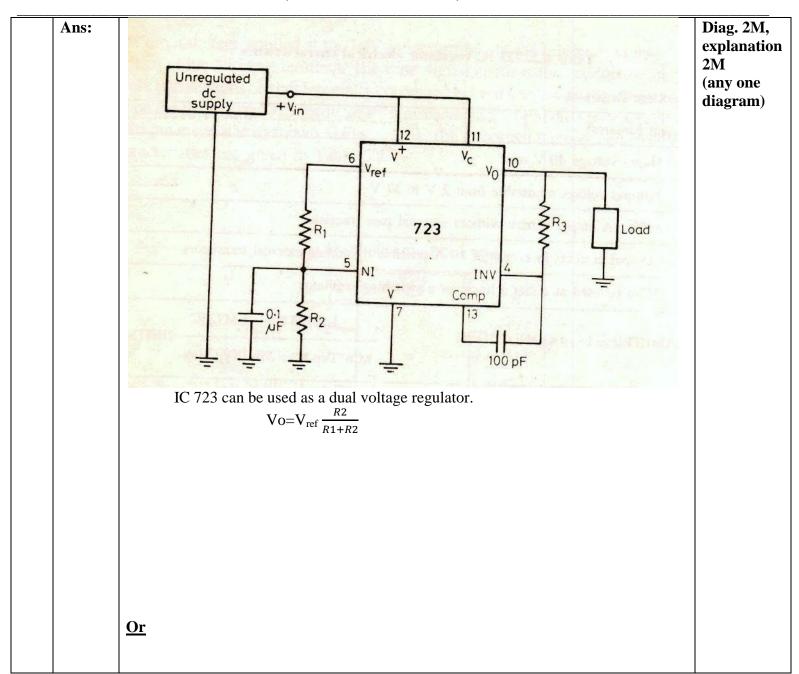

|      | Zener Diode as Voltage                                               | Regulator:                      |                                 |                                        |         |

|      | A voltage regulator circu                                            | it should keep the lo           | oad voltage consta              | ant in spite of changes in             |         |

|      | its input voltage or load c                                          | -                               | _                               |                                        |         |

|      | to limit the total current of                                        | -                               |                                 |                                        |         |

|      | regulator, as shown in fig                                           |                                 |                                 |                                        |         |

|      |                                                                      |                                 |                                 |                                        |         |

|      | element i.e. zener diode i                                           | _                               | anei with the load              | resistance.                            |         |

|      | Working of Zener Volta                                               | 0 0                             |                                 |                                        |         |

|      | The input voltage Vin is                                             | an unregulated dc v             | oltage which is ob              | otained from a rectifier               |         |

|      | filter combination. Rs is t                                          | _                               | -                               |                                        |         |

|      | input voltage Vin should                                             |                                 |                                 |                                        |         |

|      |                                                                      | •                               |                                 | _                                      |         |

|      | diode is reverse biased an                                           | iu operates in the ze           | ener region of the              | reverse characteristics, as            |         |

|      | shown in fig.(b)                                                     |                                 |                                 |                                        |         |

|      | If Vin is higher than $V_Z$ a                                        | nd if the Zener curi            | rent I <sub>Z</sub> is between  | $I_{Zmin}$ and $I_{Zmax}$ then         |         |

|      | 1                                                                    |                                 |                                 |                                        | 1       |

|      | the voltage across the Zei                                           | ner will remain con             | stant equal to V <sub>7</sub> i | rrespective of any                     |         |

|      | the voltage across the Zer<br>changes in Vin and I <sub>L</sub> . As |                                 |                                 |                                        |         |

(ISO/IEC - 27001 - 2005 Certified)

|      |            | The Zener current $I_Z$ should not be higher than $I_{Zmax}$ , otherwise excessive power dissipation will damage the Zener diode. The Zener current $I_Z$ should not be less than $I_{Zmin}$ because the Zener diode then cannot operate in the zener region and cannot maintain constant voltage across it. The regulator keeps the load voltage constant in spite of changes in input voltage and load current. |                               |

|------|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------|

| Q. 3 |            | Attempt any FOUR of the following.                                                                                                                                                                                                                                                                                                                                                                                | 16                            |

|      | a)         | Draw experimental circuit diagram and characteristics for forward biased P-N junction diode.                                                                                                                                                                                                                                                                                                                      | 4M                            |

|      | Ans:       | $\begin{array}{c c} I_f \\ \hline \\ V_s \\ \hline \\ \hline \end{array}$ $(0.200 \text{mA})$ $\downarrow V_f \\ \hline \\ $                                                                                                                                                                                                      | Each<br>Diagram:2<br>M        |

|      | <b>b</b> ) | Explain with circuit diagram fixed bias method of BJT.                                                                                                                                                                                                                                                                                                                                                            | 4M                            |

|      | Ans:       | Fixed bias (base bias)  Ib Rc LC  Vce                                                                                                                                                                                                                                                                                                                                                                             | Diagram:2 M & Explanatio n:2M |

|      |            | Fixed bias (Base bias)                                                                                                                                                                                                                                                                                                                                                                                            |                               |

|      |            | This form of biasing is also called base bias or fixed resistance biasing. The single                                                                                                                                                                                                                                                                                                                             |                               |

(Autonomous) (ISO/IEC - 27001 - 2005 Certified)

power source (for example, a battery) is used for both collector and base of a transistor, although separate batteries can also be used.

In the given circuit,

$$V_{cc} = I_B R_B + V_{be}$$

Therefore.

$$I_{B} = (V_{cc} - V_{be})/R_{B}$$

For a given transistor, V<sub>be</sub> does not vary significantly during use. As V<sub>cc</sub> is of fixed value, on selection of R<sub>B</sub>, the base current I<sub>B</sub> is fixed. Therefore, this type is called *fixed bias* type of circuit.

Also for given circuit,

$$V_{cc} = I_C R_C + V_{ce}$$

Therefore,

$$V_{ce} = V_{cc} - I_C R_C$$

$$I_C = \beta I_B$$

Thus  $I_C$  is obtained. In this manner, operating point given as  $(V_{ce}, I_C)$  can be set for given transistor.

#### Draw and explain VI characteristics of UJT. c)

#### **4M**

M &

n:2M

Diagram:2

**Explanatio**

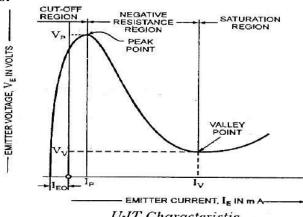

#### Ans: **UJT Characteristics:**

UJT Characteristic

The UJT characteristic is emitter voltage versus emitter current characteristic, as shown in the figure. For emitter voltages less than V<sub>P</sub> (peak point voltage) the UJT is in the off state and magnitude of I<sub>E</sub> is not greater than I<sub>EO</sub>. The emitter current I<sub>EO</sub> corresponds very closely with the reverse leakage current  $I_{CO}$  of a bipolar transistor. This region is known as the cut off region.

As the emitter voltage increases and reaches  $V_P = (\eta V_{BB} + V_D)$ , the UJT starts conducting. Then with increase in emitter IE the emitter voltage decreases as shown. The reduction in voltage across UJT is due to the drop in resistance R<sub>B1</sub> with increase in the value of I<sub>E</sub>. This region of operation is known as a "Negative Resistance" region, which is stable enough to be used in various applications. Eventually the "valley point" will be reached and further increase in I<sub>E</sub> will place the device into saturation.

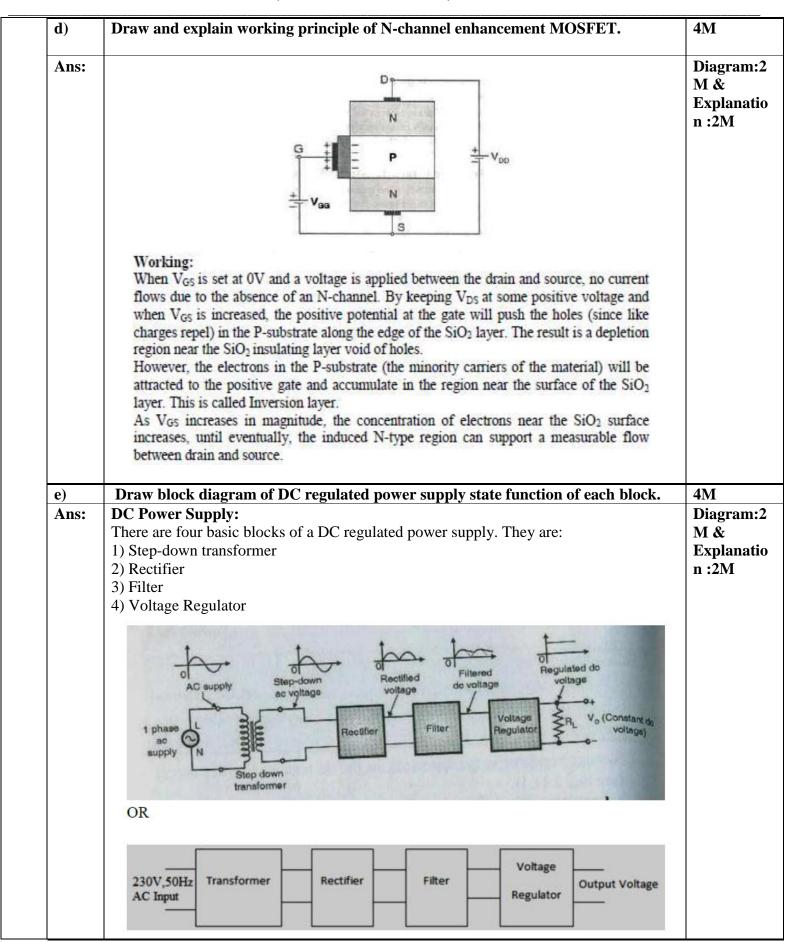

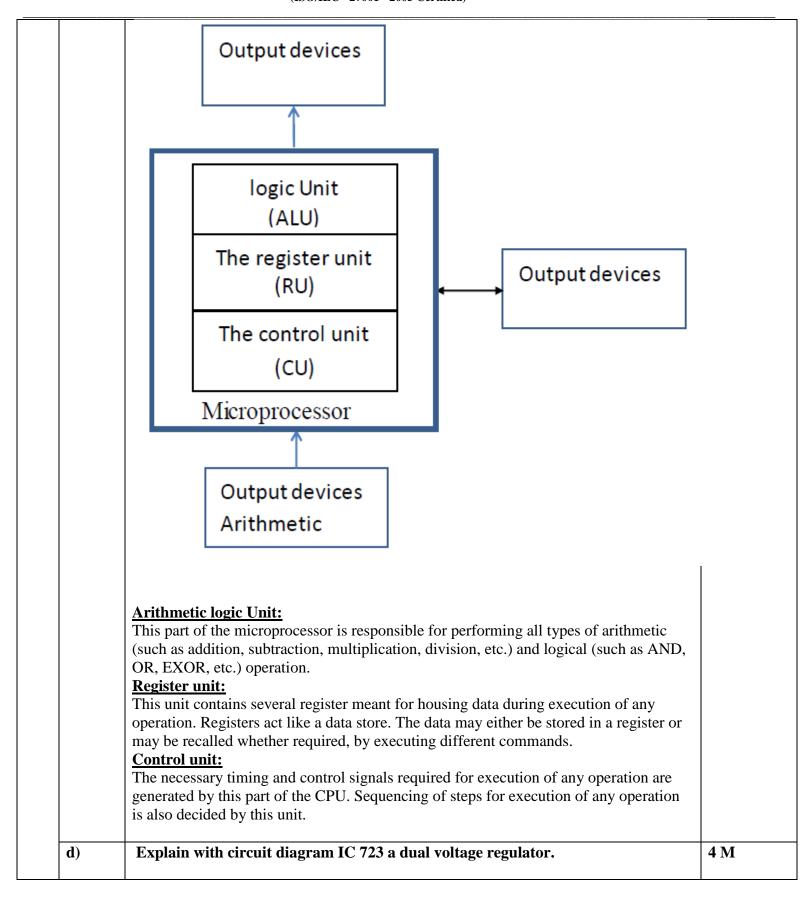

|      | Functions of Each Block:  i) Step-down transformer: Reduces 230V, 50 hz ac voltage to required ac voltage level.  ii) Rectifier: Converts ac voltage into dc voltage. Typically bridge type full-wave rectifier is widely used.  iii) Filter: Used to remove fluctuations (ripples) present in dc output.  iv) Voltage regulator: Provides constant dc output voltage irrespective of changes in load current or changes in input voltage.  Voltage divider circuit is used to provide different dc voltages required for different electronic circuits. |                         |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|

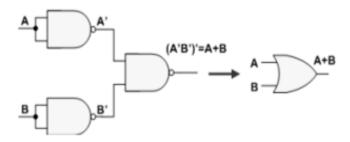

| f)   | Explain NAND gate as universal gate implement AND, OR and NOT gate using NAND gate only.                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 4M                      |

| Ans: | A universal gate(NAND) is a gate which can implement any Boolean function without need to use any other gate type.  NAND Gate is a Universal Gate: To prove that any Boolean function can be implemented using only NAND gates, we will show that the AND, OR, and NOT operations can be performed using only these gates.                                                                                                                                                                                                                               | 1M for each explanation |

(Autonomous) (ISO/IEC - 27001 - 2005 Certified)

#### Implementing an Inverter Using only NAND Gate

The figure shows two ways in which a NAND gate can be used as an inverter (NOT gate).

All NAND input pins connect to the input signal A gives an output A'.

One NAND input pin is connected to the input signal A while all other input pins are connected to logic 1. The output will be A'.

#### Implementing AND Using only NAND Gates

An AND gate can be replaced by NAND gates as shown in the figure (The AND is replaced by a NAND gate with its output complemented by a NAND gate inverter).

#### Implementing OR Using only NAND Gates

**An OR gate** can be replaced by NAND gates as shown in the figure (The OR gate is replaced by a NAND gate with all its inputs complemented by NAND gate inverters).

Thus, the NAND gate is a universal gate since it can implement the AND, OR and NOT functions.

| Q. 4 |      | Attempt any FOUR of following:        | 16 M       |

|------|------|---------------------------------------|------------|

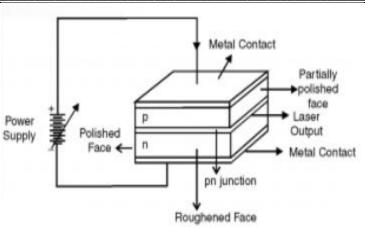

|      | a)   | Explain operating principle of LASER. | 4 M        |

|      |      |                                       |            |

|      | Ans: | LASER                                 | (Diagram:1 |

|      |      |                                       | <b>M</b> , |

|      |      |                                       | Stimulated |

|      |      |                                       | emission   |

|      |      |                                       | :2M,       |

(Autonomous) (ISO/IEC - 27001 - 2005 Certified)

# 1M)

**Operation**

## Working principle of LASER diode:

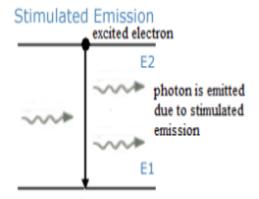

Stimulated Emission:

- In this process "amplification" of light takes place.

- If light energy strikes to the excited electron present in higher energy level, then electron will fall back to its original level.

- While returning back it will emit two photons. So one incident photon causes emission of two photons and hence light amplification takes place.

- This principle is used in LASER diode.

#### **Operation:**

- When the PN junction is forward biased by an external voltage source, electrons move across the junction and recombination occurs in the depletion region which results in the production of photons.

- As forward current is increased, more photons are produced which drift at random in depletion region.

- Some of these photons strike the reflective surface perpendicularly. These reflected photons move back and forth between two reflective surfaces as shown in fig above.

- The photon activity becomes so intense that at some point a strong beam of laser comes out of the partially reflective surface of the diode.

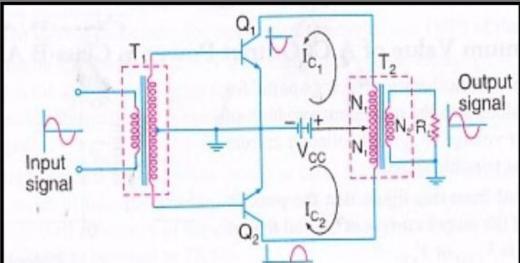

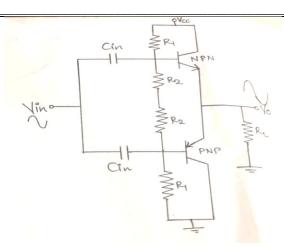

| <b>b</b> ) | Explain class B push pull power amplifier with circuit diagram. | 4 M        |

|------------|-----------------------------------------------------------------|------------|

| Ans:       | class B push pull power amplifier                               | (Diagram:2 |

|            |                                                                 | <b>M</b> , |

|            |                                                                 | Explanatio |

n: 2M)

#### MAHARASHTRA STATE BOARD OF TECHNICAL EDUCATION (Autonomous)

(ISO/IEC - 27001 - 2005 Certified)

**CIRCUIT DESCRIPTION:**

- The circuit consists of two centre tapped transformers  $T_1 \& T_2 \&$  two identical transistors  $Q_1 \& Q_2$ .

- The transformer  $T_1$  is an input transformer and is called as phase splitter. It is required to produce two signal voltages, which are 180° out of phase with each other.

- These two signal voltages with opposite polarity, drive the input of transistors  $Q_1 \& Q_{2..}$

- $\triangleright$  The transformer  $T_2$  is an output transformer and is required to couple the a.c. output signal from the collector to the load.

- The transistors  $Q_1$  and  $Q_2$  are biased at cut off.

- The two emitters are connected to the centre tap of transformer  $T_1$  secondary and the  $V_{CC}$  supply to the centre tap of transformer  $T_2$  secondary.

#### **WORKING:**

- $\triangleright$  When there is no a.c. input signal applied, both the transistors  $Q_1 \& Q_2$  are cut off. Hence no current is drawn from V<sub>CC</sub>.

- DURING POSITIVE HALF CYCLE:

- The base of the transistor  $Q_1$  is positive and that of  $Q_2$  is negative.

- As a result of this  $Q_1$  conducts, while the transistor  $Q_2$  is OFF.

- ➤ DURING NEGATIVE HALF CYCLE:

- The base of the transistor  $Q_2$  is positive and that of  $Q_1$  is negative.

- As a result of this  $Q_2$  conducts, while the transistor  $Q_1$  is OFF.

- Thus at any instant any one transistor in the circuit is conducting.

- Then the output of the transformer joins these two halves & produces a full sine wave in the load resistor.

OR

## ${\bf MAHARASHTRA~STATE~BOARD~OF~TECHNICAL~EDUCATION}$

(Autonomous) (ISO/IEC - 27001 - 2005 Certified)

#### **Circuit Description:**

- Two transistors one NPN & other PNP is used in the circuit so they are complementary to each other.

- Biasing conditions used for both transistors are same so they are symmetrical.

- R<sub>1</sub>, R<sub>2</sub>, V<sub>CC</sub> are used for voltage divider bias of transistors.

- Both transistors conduct for 180° as it is class B amplifier.

- Whenever one transistor is ON other push to be OFF so the name push pull.

#### Working:

- ➤ Input signal V<sub>in</sub> is applied to both the transistor through input capacitor.

- > During positive half cycle of input:

- The base of the transistors NPN & PNP is positive.

- As a result of this NPN conducts & PNP remains OFF.

- So we get half cycle in the output.

- > During negative half cycle of input:

- The base of the transistors NPN & PNP is negative.

- As a result of this PNP conducts & NPN remains OFF.

- So we get remaining half cycle in the output.

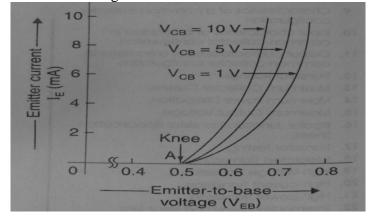

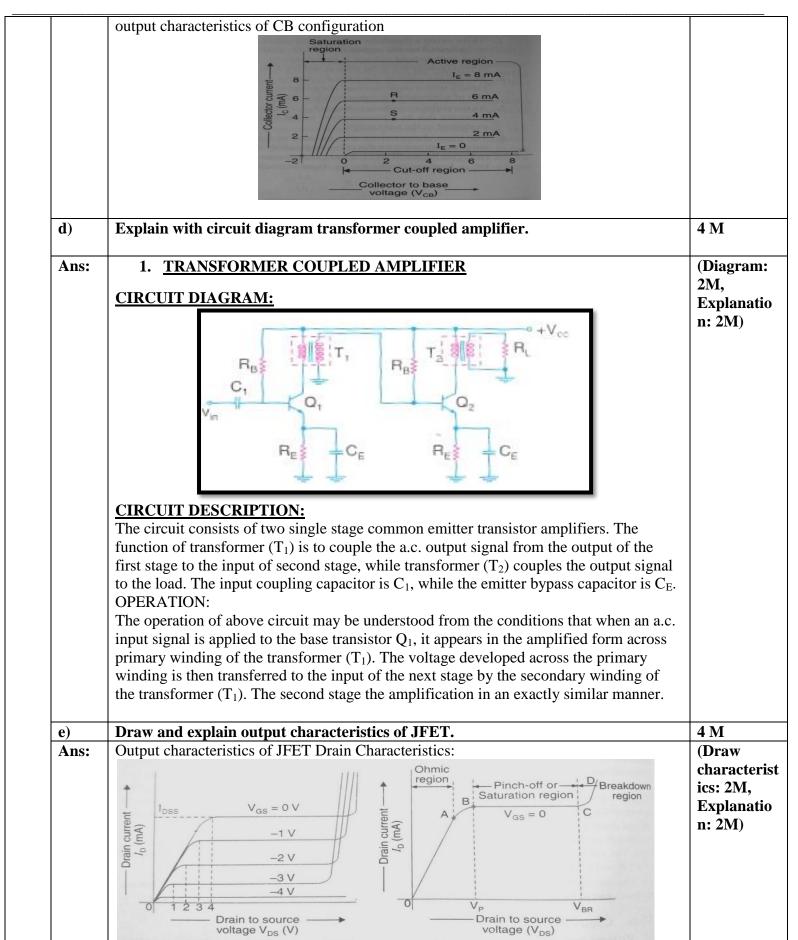

### c) Draw input and output characteristics of CB configuration.

4 M

Ans:

input characteristics of CB configuration.

(Input characterist ics: 2M, Output characterist ics: 2M)

(Autonomous) (ISO/IEC - 27001 - 2005 Certified)

- First we adjust gate to source voltage  $V_{GS}$  to zero volt. Then increase drain to source voltage  $V_{DS}$  in small suitable steps& record corresponding values of drain current  $I_D$  at each steps.

- A similar procedure may be used to obtain curves for different values of gate to source voltage  $V_{GS}$  i.e.  $V_{GS} = 1V$ , 2V, 3V & 4V.

- Now if we plot a graph with drain to source voltage V<sub>DS</sub> along horizontal axis & drain current I<sub>D</sub> along a vertical axis.

- The curve may be sub-divided into following regions:

- 1. **OHMIC REGION**: The region is shown as a curve OA in the figure. In this region drain current increases linearly with the increase in drain to source voltage, obeying Ohm's law. The linear increase in drain current is due to the fact that N-type semiconductor bar act as resistor.

- 2. CURVE AB: In this region drain current increases slowly as compared to that in ohmic region. It is because of the fact that with increase in drain to source voltage V<sub>DS</sub> drain current also increases. This in turn increases reverse bias voltage across the gate-source junction. As a result of this depletion region grows in size, thereby reducing effective width of channel. At the drain to source voltage V<sub>DS</sub> corresponding to point B, the channel width reduce to minimum value & is known as pinch off. Drain to source voltage V<sub>DS</sub> at which the channel pinch off occurs is known as pinch off voltage V<sub>P</sub>.

- 3. **PINCH OFF REGION**: The region is shown as a curve BC in the figure. It is also called as constant current region & saturation region. In this region Drain current  $I_D$  remains constant at maximum value  $I_{DSS}$ . The drain current in pinch off region is dependent on  $V_{GS}$  & it is given by Shockley's equation,  $I_D = I_{DSS} \left\{1 \frac{V_{GS}}{V_P}\right\}^2$

- 4. **BREAKDOWN REGION**: The region is shown as a curve CD in the figure. In this region drain current increases rapidly with the increase in drain to source voltage. It happens because breakdown of gate to source junction due to avalanche effect. The drain to source voltage V<sub>DS</sub> corresponding to point C is called as breakdown voltage.

# Ans: Transistorized Series Voltage regulator: Diagram.:2 M, Explanatio n: 2M

In above fig., transistor is connected in series with load therefore the circuit is known as a series regulator.

regulated

|     |      | WORK       | amount of base current. $V_L = V_Z - V_{BE}$ OR $V_{BE} = V_Z - V_{AING}$ :  Suppose that value of load resistan current decreases and load voltage From equation (1) that any increase fixed.  As a result of this the forward bias level of conduction.  This increases $V_{CE}$ of transistor whe the increase in the value of load resistance. | ce is increased. Because of this, the load $(V_L)$ tend to increase. The in $V_L$ will decrease $V_{BE}$ because $V_Z$ value is of the transistor is reduced which reduces its will slightly decrease the input current for sistance so that load voltage remains constant. Solution is approximately equal to zone voltage |                   |

|-----|------|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|

| Q.5 |      |            | pt any <u>FOUR</u> of following:                                                                                                                                                                                                                                                                                                                   | larger load currents.                                                                                                                                                                                                                                                                                                       | 16 M              |

| Q.S | a)   |            | are BJT with FET (any 4 pts.).                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                             | 4 M               |

|     | Ans: | SR.<br>NO. | FET                                                                                                                                                                                                                                                                                                                                                | ВЈТ                                                                                                                                                                                                                                                                                                                         | 1m Each<br>(Any 4 |

|     |      | 2          | It is unipolar device i.e. current in the device is carried either by electrons or holes  It is a voltage controlled device i.e. voltage at the gate (or drain) terminal controls amount of current flowing through the device.                                                                                                                    | It is bipolar device i.e. current in the device is carried either by both electrons & holes  It is a current controlled device i.e. the base current controls the amount of collector current.                                                                                                                              | Points)           |

|     |      | 3          | Its input resistance is very high & is of order of several megaohms.                                                                                                                                                                                                                                                                               | Its input resistance is very low compared to FET.                                                                                                                                                                                                                                                                           |                   |

|     |      | 4          | It has a negative temperature co-efficient at high current levels. It means that current decreases as temperature increases.                                                                                                                                                                                                                       | It has a positive temperature coefficient at high current levels. It means that current increases as temperature increases.                                                                                                                                                                                                 |                   |

|     |      | 5          | It is less noisy.                                                                                                                                                                                                                                                                                                                                  | It is comparatively noisier.                                                                                                                                                                                                                                                                                                |                   |

|     |      | 6          | It has relatively lower gain bandwidth product as compared to BJT.                                                                                                                                                                                                                                                                                 | It has relatively higher gain bandwidth product as compared to FET.                                                                                                                                                                                                                                                         |                   |

|     |      | 7          | It is simpler to fabricate as IC & occupies less space on chip compared to BJT.                                                                                                                                                                                                                                                                    | It is comparatively difficult to fabricate on IC & occupies more space on chip compared to FET.                                                                                                                                                                                                                             |                   |

|     |      | 8          | It is relatively immune to radiation.                                                                                                                                                                                                                                                                                                              | It is susceptible to radiation                                                                                                                                                                                                                                                                                              |                   |

|     |      | 9          | It does not suffer from minority- carrier storage effects & therefore has higher switching speeds & cut-off                                                                                                                                                                                                                                        | It suffers from minority- carrier storage effects & therefore has lower switching speeds & cut-off frequencies.                                                                                                                                                                                                             |                   |

(ISO/IEC - 27001 - 2005 Certified)

|            | frequencies.                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                  |

|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------|

| <b>b</b> ) | State the need of multistage amplifier. Draw frequency response of R-C coupled amplifier.                                                                                                                                                                                                                                                                                                                                            | 4 M                                              |

| Ans:       | The need of multistage amplifier  The voltage (or power) gain, obtained from a single stage small signal amplifier, is limited. Therefore, it is not sufficient for all practical applications. Therefore, in order to obtain greater voltage and power gain, we have to use a 'MULTISTAGE AMPLIFIER'.  Frequency response of R-C coupled amplifier.  High frequency Roll off  Flat response  High frequency Roll off  Frequency (f) | Need 2M,<br>frequency<br>response<br>2M          |

| <b>c</b> ) | Draw circuit diagram of voltage divider biasing list two advantages of voltage divider biasing of BJT.                                                                                                                                                                                                                                                                                                                               | 4 M                                              |

| Ans:       | circuit diagram of voltage divider biasing of BJT $ \begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                             | Circuit<br>diagram<br>2M, each<br>advantag<br>1M |

|            | <ol> <li>Two advantages of voltage divider biasing of BJT.</li> <li>It is very simple method of transistor biasing.</li> <li>The biasing conditions can be very easily set.</li> <li>there is no loading of source</li> <li>It provides better bias stabilization.</li> <li>The resistor R<sub>E</sub> introduces a negative feedback. So all the advantages of negative feedback are obtained.</li> </ol>                           |                                                  |

|            |                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                  |

(Autonomous) (ISO/IEC - 27001 - 2005 Certified)

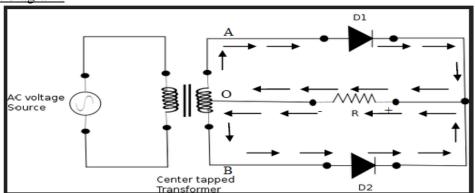

Ans:

#### Full wave Rectifier with Center tapped transformer(FWR):

In full wave rectification, the rectifier conducts in both the cycles as two diodes are connected.

Circuit diagram:

- The circuit employs two diodes D1 and D2 as shown. A center tapped secondary winding AB is used with two diodes connected. So that each uses one half –cycles of input AC voltage.

- Diode D1 utilized the AC voltage appearing across the upper half (OA), while diode D2 uses the lower half winding (OB).

- The voltage  $V_s$  between the center-tap and either ends of secondary winding is half of the secondary voltage  $V_2$ i.e $V_s = \frac{V_2}{2}$

- If the output voltage should be equal to the input voltage, a step up transformer with turns ratio  $\frac{N_2}{N_1} = 2$  must be used. Thus the total secondary voltage  $V_2$  is twice the primary voltage.

i.e,

$$V_s = V_1 = \frac{V_2}{2}$$

#### Operation:

- 1. In positive half cycle  $(0-\Pi)$ .

- The end A of the secondary winding becomes positive and end B negative.

- This makes diode D<sub>1</sub> forward biased and diode D<sub>2</sub> reverse biased. Therefore D<sub>1</sub> conducts while D<sub>2</sub> does not.

- The conventional current flow direction in the upper half winding as shown in the fig above.

$$A - D_1 - R_L - O$$

- 2. In negative half cycle ( $\Pi$ -2 $\Pi$ ):

- End A of secondary winding becomes negative and end B positive. Therefore diode D<sub>2</sub> conducts while diode D<sub>1</sub> does not.

- The conventional current flow is as shown by the arrows in the above fig.

$$B - D_2 - R_L - O$$

From fig. current in the load R<sub>L</sub> is in the same direction for both half-cycles of input AC voltage. Therefore DC is obtained across the load R<sub>L</sub>. Circuit

Diagram

2M, Input

Output

Waveform

1M,

Explanatio

n 1M

## ${\bf MAHARASHTRA~STATE~BOARD~OF~TECHNICAL~EDUCATION}$

(Autonomous) (ISO/IEC - 27001 - 2005 Certified)

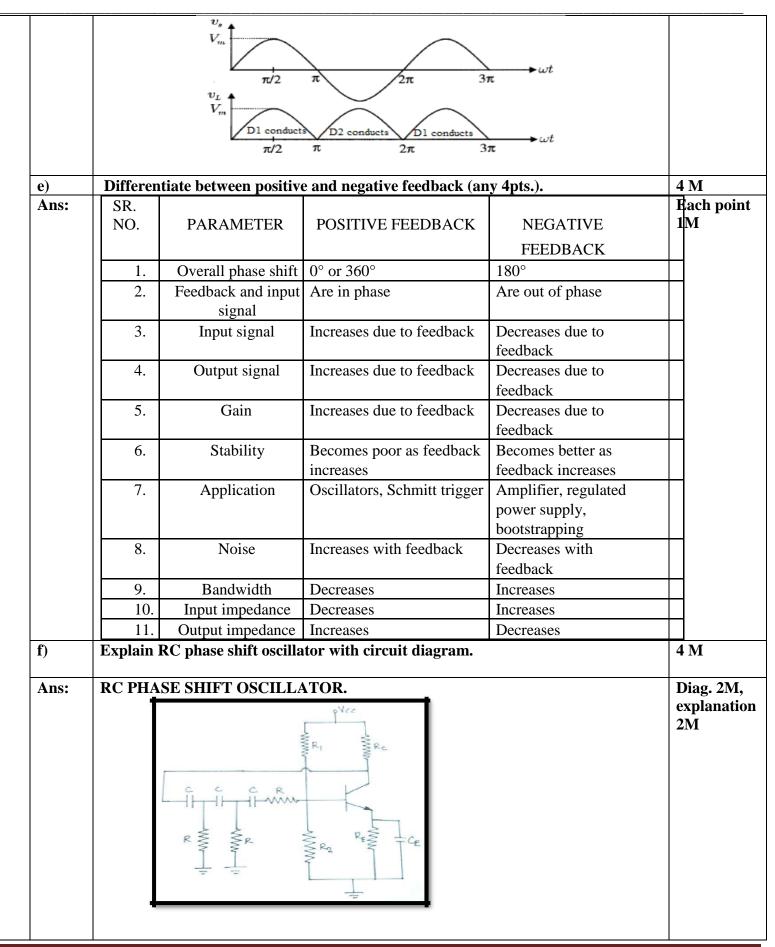

| • | Circuit | consists   | of   | a    | single    | stage   | amplifier | in | common | emitter |

|---|---------|------------|------|------|-----------|---------|-----------|----|--------|---------|

|   | configu | ration & R | C pl | hase | e shiftin | g netwo | ork.      |    |        |         |

• R<sub>1</sub>, R<sub>2</sub>, R<sub>E</sub> provides biasing & C<sub>E</sub> is bypass capacitor.

#### **WORKING**:

- Common emitter amplifier introduces 180<sup>0</sup> phase shift between input &output.

& remaining 180<sup>0</sup> phase shift is produced by three identical basic RC phase shifting networks.

- Each RC network is designed to introduce a phase shift of  $60^{\circ}$ .

- The phase shift around the loop is 360<sup>0</sup> only at one precise frequency.

- This frequency of oscillations is equal to  $\frac{1}{2\pi RC\sqrt{6}}$

- The feedback factor  $\beta = \frac{1}{29}$ Therefore  $A_v = 29$ .

|            | Attempt any FOUR of following:                                                                    | 16 M |

|------------|---------------------------------------------------------------------------------------------------|------|

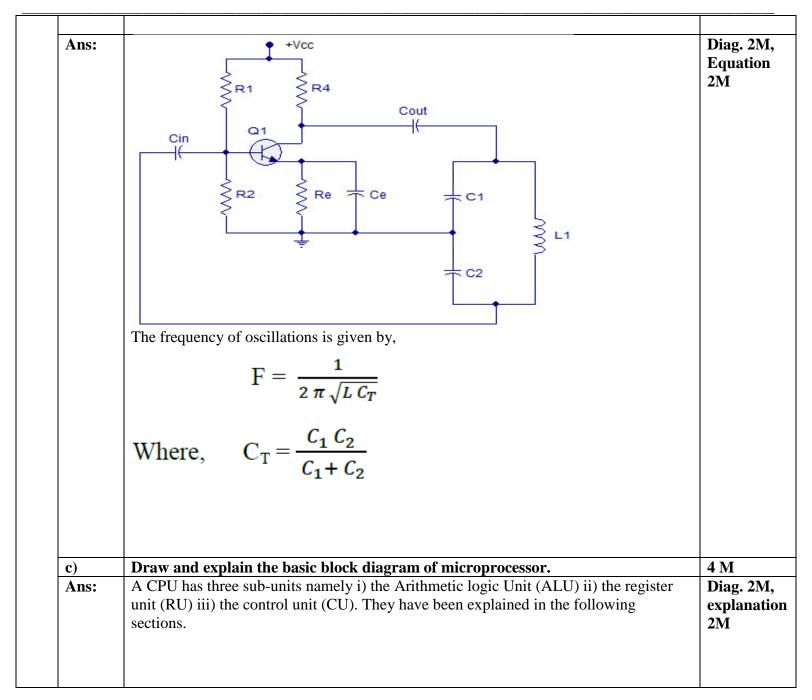

| a)         | For Hartley oscillator $C=2$ nF, $L=5.6$ mH, $Lz=56$ $\mu$ H. Calculate frequency of oscillation. | 4 M  |

| Ans:       | Given data- C= 2nF                                                                                |      |

|            | L1 = $5.6$ mH<br>L2 = $56 \mu$ H                                                                  |      |

|            | Frequency of oscillation is given as                                                              |      |

|            | $Fo = \frac{1}{2 \pi \sqrt{L_T \cdot C}}$                                                         |      |

|            | $L_T = L_1 + L_2 = 5.656 \text{ mH}$                                                              |      |

|            | $L_T = L_1 + L_2 = 5.656 \text{ mH}$ $F_0 = \frac{1}{2\pi\sqrt{5.656*10^{-3}*2*10^{-9}}}$         |      |

|            | $=47.320 \text{ KH}_{z}$                                                                          |      |

| <b>b</b> ) | Draw circuit diagram of Colpitts Oscillator. State its frequency of oscillation equation.         | 4 M  |

(ISO/IEC - 27001 - 2005 Certified)

(ISO/IEC - 27001 - 2005 Certified)

(ISO/IEC - 27001 - 2005 Certified)

#### Ans:

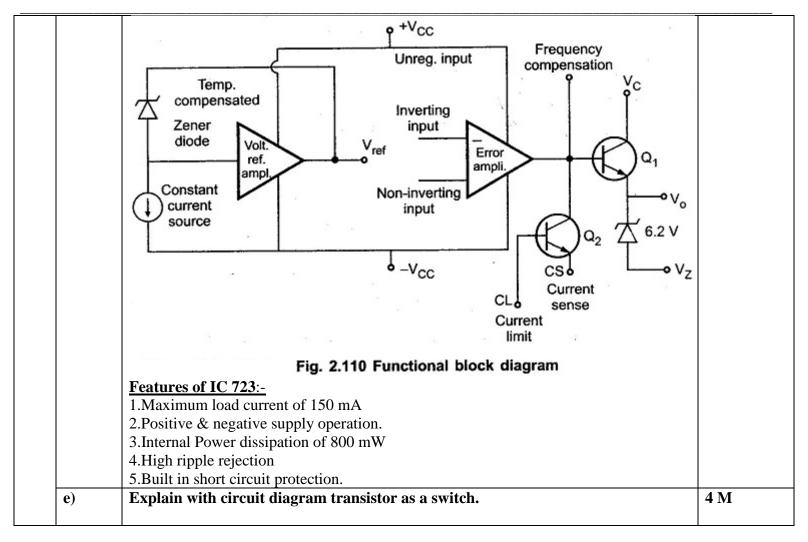

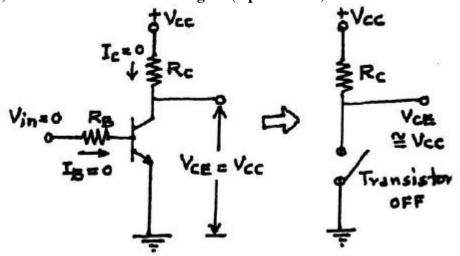

#### **Transistor as Switch:**

A transistor can be used for two types of applications viz. amplification and switching. For amplification, the transistor is biased in its active region.

For switching applications, transistor is biased to operate in the saturation (full on) or cut-off (full off) region.

( OFF condition: diagram = 1 marks, explanation = 1 mark

#### (i) Transistor in cut-off region (Open switch):

In the cur-off region, both the junctions of transistor are reverse biased and very small reverse current flows through the transistor.

The voltage drop across the transistor (VCE) is high, nearly equal to supply voltage VCC. Thus, in cut-off region the transistor is equivalent to an open switch as shown in above fig.

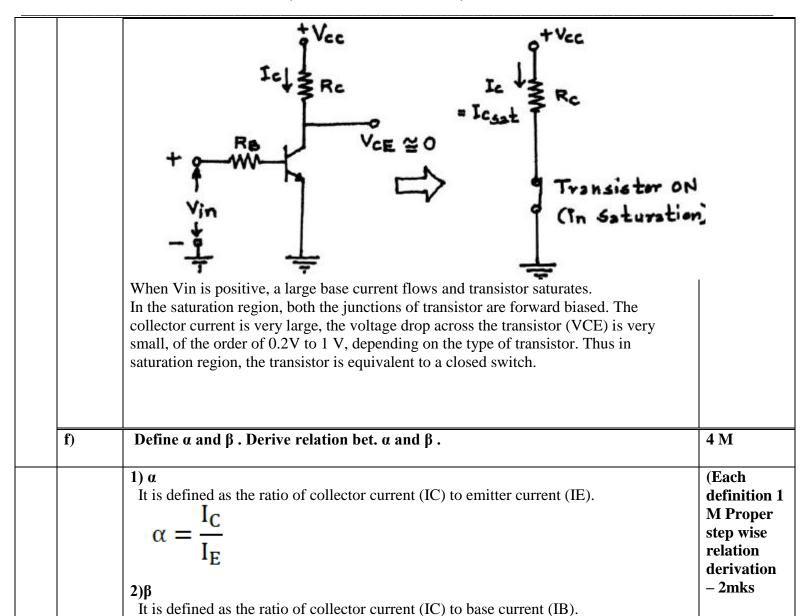

ii)Transistor in Saturation region (Closed switch):

ON condition: diagram = 1 marks, explanation = 1 mark

(Autonomous) (ISO/IEC - 27001 - 2005 Certified)

## Relation between α and β:

Current gain of transistor in CB configuration is,

$$\alpha = \frac{I_C}{I_E}$$

But  $I_E = I_B + I_C$

$$\alpha = \frac{I_C}{I_B + I_C}$$

Dividing numerator and denominator by IB,

$$\alpha = \frac{\frac{I_C}{I_B}}{1 + \frac{I_C}{I_B}}$$

But  $\beta = \frac{I_C}{I_B}$  the current gain of transistor in CE configuration.

Therefore,

$$\alpha = \frac{\beta}{1+\beta}$$

OR

Current gain of transistor in CE configuration is,

$$\beta = \frac{I_C}{I_B}$$

But  $I_E = I_B + I_C$ , so  $I_B = I_E - I_C$

$$\beta = \frac{I_C}{I_E - I_C}$$

Dividing numerator and denominator by IE,

$$\beta = \frac{\frac{I_C}{I_E}}{1 - \frac{I_C}{I_E}}$$

But  $\alpha = \frac{I_C}{I_E}$  the current gain of transistor in CE configuration. Therefore,

$$\beta = \frac{\alpha}{1-\alpha}$$