### SUMMER- 18 EXAMINATION Model Answer

Subject Name: Micro controller

Subject Code:

17534

### Important Instructions to examiners:

- 1) The answers should be examined by key words and not as word-to-word as given in the model answer scheme.

- 2) The model answer and the answer written by candidate may vary but the examiner may try to assess the understanding level of the candidate.

- 3) The language errors such as grammatical, spelling errors should not be given more Importance (Not applicable for subject English and Communication Skills.

- 4) While assessing figures, examiner may give credit for principal components indicated in the figure. The figures drawn by candidate and model answer may vary. The examiner may give credit for any equivalent figure drawn.

- 5) Credits may be given step wise for numerical problems. In some cases, the assumed constant values may vary and there may be some difference in the candidate's answers and model answer.

- 6) In case of some questions credit may be given by judgement on part of examiner of relevant answer based on candidate's understanding.

- 7) For programming language papers, credit may be given to any other program based on equivalent concept.

| Q.<br>No. | Sub<br>Q.<br>N. |           |                                | Answers                                                                                                         |                                                                                                                                                                                                                                          | Marking<br>Scheme  |

|-----------|-----------------|-----------|--------------------------------|-----------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|

| 1         | а               | Atter     | npt any THREE:                 |                                                                                                                 |                                                                                                                                                                                                                                          | 12- Total<br>Marks |

|           | i               | Comp      | oare between mi                | croprocessor and microcontro                                                                                    | ller (any four points).                                                                                                                                                                                                                  | 4M                 |

|           | Ans:            |           |                                |                                                                                                                 |                                                                                                                                                                                                                                          | 1Mark each         |

|           |                 | Sr.<br>No | Parameter                      | Microprocessor                                                                                                  | Microcontroller                                                                                                                                                                                                                          |                    |

|           |                 | 1         | No. of<br>instructions<br>used | Many instructions to<br>read/write data to/ from<br>external memory.                                            | Few instruction to read/<br>write data to/ from external<br>memory                                                                                                                                                                       |                    |

|           |                 | 2         | Memory                         | Do not have inbuilt RAM or ROM.                                                                                 | Inbuilt RAM /or ROM                                                                                                                                                                                                                      |                    |

|           |                 | 3         | Registers                      | Microprocessor contains<br>general purpose<br>registers,<br>Stack pointer register,<br>Program counter register | Microcontroller contains<br>general purpose registers,<br>Stack pointer register,<br>Program counter register<br>additional to that it contains<br>Special Function Registers<br>(SFRs) for Timer, Interrupt<br>and serial communication |                    |

### **SUMMER-18 EXAMINATION**

Subject Name: Micro controller

Model Answer

Subject Code:

|      |      |                       |                                                                                     | etc.                                                                                                               |    |

|------|------|-----------------------|-------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------|----|

|      | 4    | Timer                 | Do not have inbuilt<br>Timer.                                                       | Inbuilt Timer                                                                                                      |    |

|      | 5    | I/O ports             | I/O ports are not<br>available requires extra<br>device like 8155 or 8255.          | I/O ports are available                                                                                            |    |

|      | 6    | Serial port           | Do not have inbuilt serial<br>port, requires extra<br>devices like 8250 or<br>8251. | Inbuilt serial port                                                                                                |    |

|      | 7    | Multifunction pins    | Less Multifunction pins on IC.                                                      | Many multifunction pins on the IC                                                                                  |    |

|      | 8    | Boolean<br>Operation  | Boolean operation is not possible directly.                                         | Boolean Operation i.e.<br>operation on individual bit is<br>possible<br>directly                                   |    |

|      | 9    | Applications          | General purpose,<br>Computers and Personal<br>Uses.                                 | Single purpose(dedicated<br>application), Automobile<br>companies, embedded<br>systems, remote control<br>devices. |    |

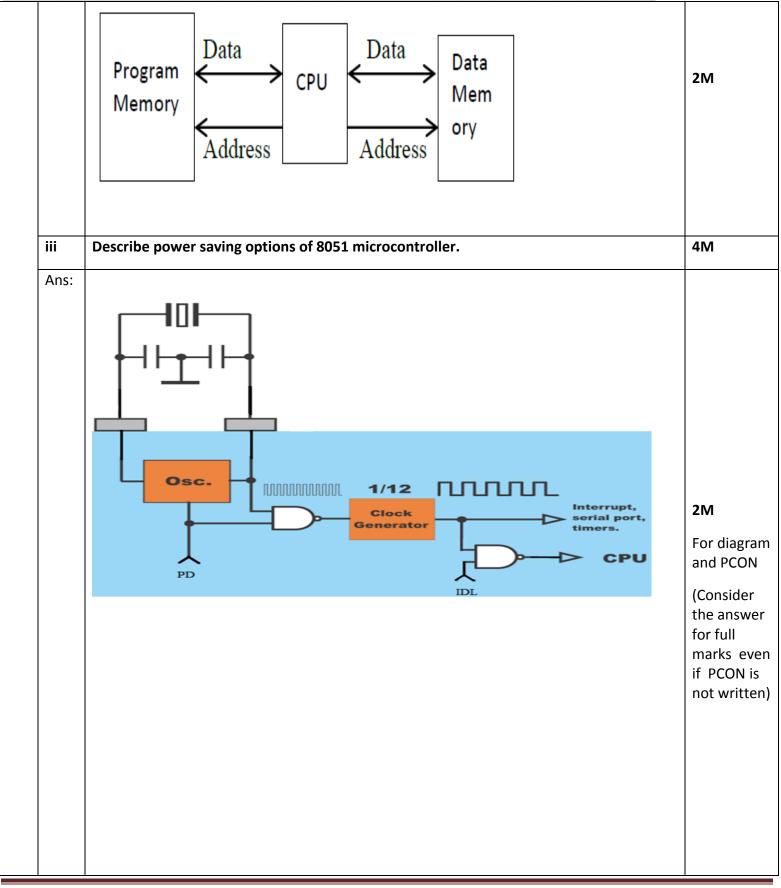

| ii   | Draw | v neat labelled block | diagram of Von-neumann                                                              | and Harvard architecture.                                                                                          | 4M |

| Ans: |      | CPU <                 | ata<br>ddress                                                                       | lata                                                                                                               | 2М |

|      | Harv | ard Architecture      |                                                                                     |                                                                                                                    |    |

### **SUMMER-18 EXAMINATION**

Subject Name: Micro controller

Model Answer

17534

# SUMMER- 18 EXAMINATION Model Answer

Subject Name: Micro controller

Subject Code:

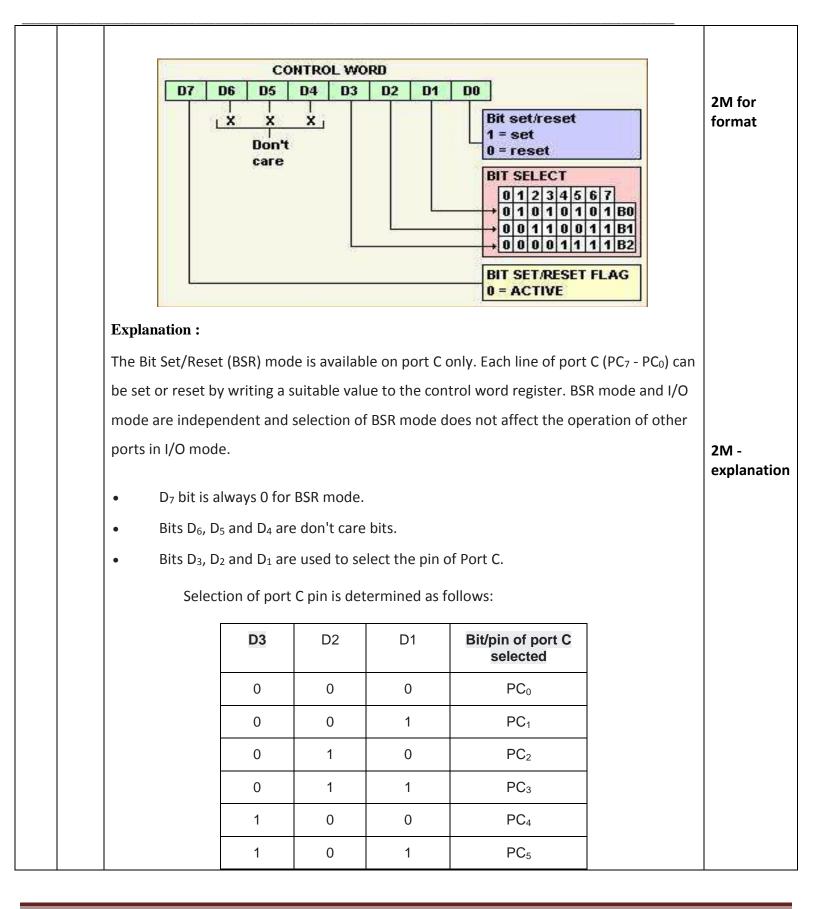

|            | SMOD       | -             | -            | -            | GF1                       | GF0          | PD         | IDI         |         |             |        |

|------------|------------|---------------|--------------|--------------|---------------------------|--------------|------------|-------------|---------|-------------|--------|

| SMOI       | Dauble be  |               | IC Times     | 1 in more da | b                         |              | SUOD -     | 1 db - ba   |         | in daarki a |        |

| 5/101      |            |               |              | modes 1,     | to generate b<br>2, or 3. | iud rate and | SMOD -     | - i, ine ba | ud rate | is double   |        |

| -          | Not imple  | emented, re   | served for   | future use   | •                         |              |            |             |         |             | 11     |

| -          | •          |               |              | future use   |                           |              |            |             |         |             |        |

| —          | •          |               |              | future use   | •                         |              |            |             |         |             |        |

| GF1        | General p  | -             |              |              |                           |              |            |             |         |             |        |

| GF0<br>PD  | General p  | -             |              | hit activat  | es Power Do               | wa operatio  | n in tha Q | 005100      |         |             |        |

| PD         | Power Do   | own on. S     | tung uns     | on activat   | to rower Do               | wii operatio | n in the e | ocondri.    |         |             |        |

| IDL        | Idle Mode  | e bit. Settir | g this bit a | ctivates Id  | le Mode oper              | ation in the | 80C51BH.   |             |         |             |        |

|            |            |               |              |              |                           |              |            |             |         |             |        |

| IDLE MC    | DE         |               |              |              |                           |              |            |             |         |             |        |

| In the Id  | le mode,   | the inte      | ernal clo    | ck signa     | l is gated                | off to the   | CPU, b     | ut not to   | the l   | nterrup     | pt,    |

| Timer, a   | nd Serial  | Port fui      | nctions.     |              |                           |              |            |             |         |             |        |

| The CPU    | status is  | preserv       | ed in its    | s entiret    | y, the Sta                | ck Pointe    | r, Progra  | am Cour     | nter, F | rogram      | n      |

| Status W   | /ord, Acc  | umulate       | or, and a    | all other    | registers                 | maintain     | their da   | ita durir   | g Idle  | . The       |        |

| port pin:  | s hold the | e logical     | state th     | ney had      | at the tim                | e idle mo    | de was     | activate    | d. ALE  | Eand        |        |

| PSEN ho    | ld at logi | c high le     | vels.        |              |                           |              |            |             |         |             |        |

| There ar   | e two wa   | ays to te     | rminate      | the idle     | e mode.                   |              |            |             |         |             |        |

| i) Activa  | tion of ar | ny enabl      | ed inter     | rupt wil     | l cause PC                | ON.O to      | be clear   | ed and i    | dle m   | ode is      |        |

| terminat   | ted.       |               |              |              |                           |              |            |             |         |             |        |

| ii) Hard v | ware rese  | et: that      | s signal     | at RST p     | oin clears                | DEAL bit     | IN PCOI    | N registe   | er dire | ctly. At    | t   1N |

| this time  | e, CPU res | sumes t       | ne prog      | ram exe      | cution fro                | m where      | it left o  | ff.         |         |             |        |

| POWER      | DOWNN      | /IODE         |              |              |                           |              |            |             |         |             |        |

| An instru  | uction the | at sets F     | CON.1        | causes t     | hat to be <sup>.</sup>    | he last ir:  | structio   | on execu    | ted b   | efore       |        |

|            |            |               |              |              |                           |              |            |             |         |             |        |

| aning int  | the be     | WOR LION      | wn mad       | o ln +ho     | Dowor D                   | own mod      | o tho o    | n chin a    | coillat | oric        |        |

# SUMMER- 18 EXAMINATION Model Answer

Subject Name: Micro controller

Subject Code:

|      | stopped. With the clock frozen, all functions are stopped, but the on-chip RAM and               |                    |

|------|--------------------------------------------------------------------------------------------------|--------------------|

|      | Special Function Register are maintained held. The port pins output the values held by           |                    |

|      | their respective SFRS. ALE and PSEN are held low.                                                |                    |

|      | Termination from power down mode: an exit from this mode is hardware reset.                      |                    |

|      | Reset defines all SFRs but doesn't change on chip RAM                                            | 1M                 |

|      |                                                                                                  |                    |

| iv   | Write the operation of the following instructions of 8051.                                       | 4M                 |

|      | 1) CJNE A, direct, rel                                                                           |                    |

|      | 2) DAA                                                                                           |                    |

|      | 3) DJNZ Rn, rel.                                                                                 |                    |

|      | 4) SWAP A                                                                                        |                    |

|      |                                                                                                  |                    |

| Ans: |                                                                                                  |                    |

|      | 1) CJNE A, direct, rel                                                                           | 1M for             |

|      | Compare the contents of the accumulator with the 8 bit data in memory address                    | each<br>instructio |

|      | mentioned in the instruction and if they are not equal then jump to the relative address         | with               |

|      | mentioned in the instruction.                                                                    | example            |

|      | Example: CJNE A, 04H, UP                                                                         |                    |

|      | Compare the contents of the accumulator with the contents of 04H memory and if they              |                    |

|      | are not equal then jump to the line of instruction where UP label is mentioned.                  |                    |

|      | 2) DA A (Decimal Adjust After Addition).                                                         |                    |

|      | When two BCD numbers are added, the answer is a non-BCD number. To get the result in             |                    |

|      | BCD, we use DA A instruction after the addition.                                                 |                    |

|      | DA A works as follows.                                                                           |                    |

|      | • If lower nibble is greater than 9 or auxiliary carry is 1, 6 is added to lower nibble.         |                    |

|      | <ul> <li>If upper nibble is greater than 9 or carry is 1, 6 is added to upper nibble.</li> </ul> |                    |

|      | Eg 1: MOV A,#23H                                                                                 |                    |

|      | MOV R1,#55H                                                                                      |                    |

### **SUMMER-18 EXAMINATION**

Subject Name: Micro controller Model Answer

Subject Code:

|      | ADD A, R1 // [A]=78 H                                                                       |    |

|------|---------------------------------------------------------------------------------------------|----|

|      | DA A // [A]=78 no changes in the accumulator after da a                                     |    |

|      | <b>Eg 2</b> : MOV A,#53H                                                                    |    |

|      | MOV R1,#58H                                                                                 |    |

|      | ADD A,R1 // [A]=ABh                                                                         |    |

|      | DA A // [A]=11, C=1 . ANSWER IS 111. Accumulator data is changed after DA A                 |    |

|      | 3) DJNZ Rn, rel.(Decrement and jump if not zero)                                            |    |

|      | In this instruction a byte present in register Rn is decremented, and if the result is not  |    |

|      | zero it will jump to the relative address mentioned in the instruction.                     |    |

|      | Example: DJNZ R3, HERE                                                                      |    |

|      | Decrements the contents of the register R3, and if it is not equal to zero then jump to the |    |

|      | line of instruction where HERE label is mentioned.                                          |    |

|      | 4) SWAP A                                                                                   |    |

|      | Description: This instruction exchanges bits 0-3 of the Accumulator with bits 4-7 of the    |    |

|      | Accumulator. This instruction is identical to executing "RR A" or "RL A" four times.        |    |

|      | No of bytes: 1 byte                                                                         |    |

|      | Addressing mode: register specific                                                          |    |

|      | Example: MOV A, #59H ; A= 59H                                                               |    |

|      | SWAP A ; A= 95H                                                                             |    |

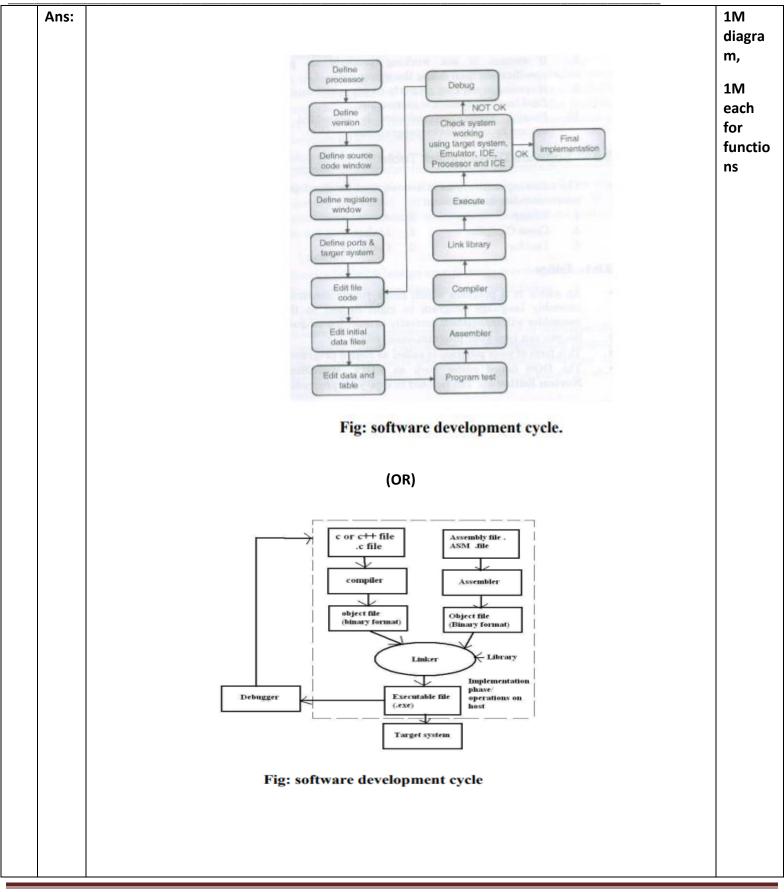

| v    | With control word register, explain Bit Set reset (BSR) mode of 8255.                       | 4M |

| Ans: |                                                                                             |    |

|      |                                                                                             |    |

|      |                                                                                             |    |

|      |                                                                                             |    |

|      |                                                                                             |    |

|      |                                                                                             |    |

|      |                                                                                             |    |

|      |                                                                                             |    |

### SUMMER- 18 EXAMINATION Model Answer

Subject Name: Micro controller

17534

# SUMMER- 18 EXAMINATION Model Answer

Subject Name: Micro controller

Subject Code:

|      |                                                                                                                                                                                                                                                                                                                                          |                                        | 1              | 1          | 0                        | PC <sub>6</sub>                  |                |                |                   |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|----------------|------------|--------------------------|----------------------------------|----------------|----------------|-------------------|

|      |                                                                                                                                                                                                                                                                                                                                          |                                        | 1              | 1          | 1                        | PC <sub>7</sub>                  |                |                |                   |

|      | • Bit I                                                                                                                                                                                                                                                                                                                                  | $D_0$ is used to                       | o set/res      | et the sel | lected pin of            | Port C.                          |                |                |                   |

|      | As an example, if it is needed that $PC_5$ be set, then in the control word,                                                                                                                                                                                                                                                             |                                        |                |            |                          |                                  |                |                |                   |

|      | <ol> <li>Since it is BSR mode, D<sub>7</sub> = '0'.</li> <li>Since D<sub>4</sub>, D<sub>5</sub>, D<sub>6</sub> are not used, assume them to be '0'.</li> <li>PC<sub>5</sub> has to be selected, hence, D<sub>3</sub> = '1', D<sub>2</sub> = '0', D<sub>1</sub> = '1'.</li> <li>PC<sub>5</sub> has to be set, hence, D0 = '1'.</li> </ol> |                                        |                |            |                          |                                  |                |                |                   |

|      |                                                                                                                                                                                                                                                                                                                                          |                                        |                |            |                          |                                  |                |                |                   |

|      |                                                                                                                                                                                                                                                                                                                                          |                                        |                |            |                          |                                  |                |                |                   |

|      |                                                                                                                                                                                                                                                                                                                                          |                                        |                |            |                          |                                  |                |                |                   |

|      | Thus, as per the above values, OB (Hex) will be loaded into the Control Word Register (CWR).                                                                                                                                                                                                                                             |                                        |                |            |                          |                                  |                |                |                   |

|      | D <sub>7</sub>                                                                                                                                                                                                                                                                                                                           | D <sub>6</sub>                         | D <sub>5</sub> | D4         | D <sub>3</sub>           | D <sub>2</sub>                   | D <sub>1</sub> | D <sub>0</sub> |                   |

|      | 0                                                                                                                                                                                                                                                                                                                                        | 0                                      | 0              | 0          | 1                        | 0                                | 1              | 1              |                   |

| b    | Attempt ar                                                                                                                                                                                                                                                                                                                               | ny ONE:                                |                |            |                          |                                  |                |                | 6- Total<br>Marks |

| i    |                                                                                                                                                                                                                                                                                                                                          | AM location                            |                |            |                          | verage of ten<br>Is store result |                |                | 6M                |

| Ans: |                                                                                                                                                                                                                                                                                                                                          |                                        |                |            |                          |                                  |                |                |                   |

|      | ORG 0000H                                                                                                                                                                                                                                                                                                                                |                                        |                |            |                          |                                  |                |                |                   |

|      | MOV R1, #0A ;R1 stores the count of total 8 bit numbers                                                                                                                                                                                                                                                                                  |                                        |                |            |                          |                                  |                |                | 6M for<br>correct |

|      | MOV B, #0A ;B is used as divisor for average                                                                                                                                                                                                                                                                                             |                                        |                |            |                          |                                  |                |                |                   |

|      |                                                                                                                                                                                                                                                                                                                                          |                                        |                |            |                          |                                  |                |                |                   |

|      | МС                                                                                                                                                                                                                                                                                                                                       | DV B, #0A<br>DV R0, #30H<br>DV A, #00H | I              |            | R0 acts as po<br>Clear A | inter to the da                  | ata            |                |                   |

### SUMMER-18 EXAMINATION

Subject Name: Micro controller <u>Model Answer</u>

Subject Code:

|      |                   | INC RO                                          | ; Increment the pointer                                                                                                                                                                                                |    |

|------|-------------------|-------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|      |                   | DJNZ R1,BACK                                    | ; repeat addition until R1=0                                                                                                                                                                                           |    |

|      |                   | DIV AB                                          | ; divide sum to get average                                                                                                                                                                                            |    |

|      |                   |                                                 | ; quotient is in A and remainder in B                                                                                                                                                                                  |    |

|      |                   | MOV 60H,A                                       | ;Ignore remainder and store average result in 60h                                                                                                                                                                      |    |

|      | HERE:             | SJMP HERE                                       | ; wait                                                                                                                                                                                                                 |    |

|      |                   | END                                             |                                                                                                                                                                                                                        |    |

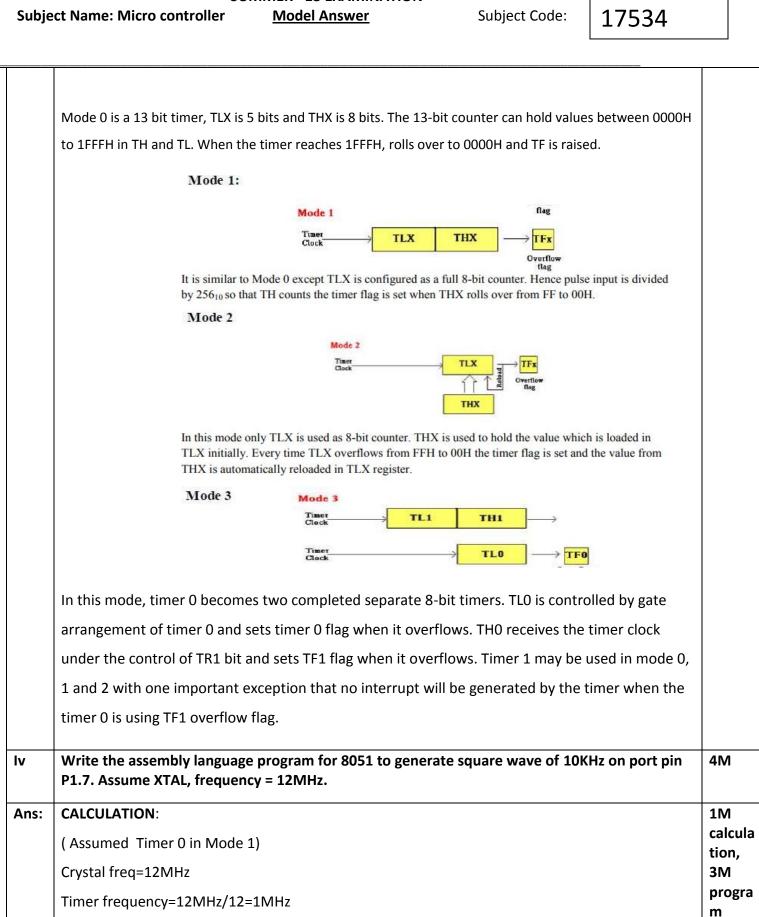

| ii   | Sketch<br>Interfa | 8051 microcontroller<br>ice LEDs to port 0 uppe | ge. Please check the logic and understanding of students.<br>interfacing diagram to interface 4 LEDs and 4 switches.<br>er nibble and switch to port 1. Write an ALP for 8051 to<br>operate LEDs as per switch status. | 6M |

| Ans: |                   |                                                 |                                                                                                                                                                                                                        |    |

|      |                   | ca ny                                           |                                                                                                                                                                                                                        |    |

|      |                   |                                                 |                                                                                                                                                                                                                        | 3М |

|      | Progra            |                                                 |                                                                                                                                                                                                                        | 3М |

|      | Progra            | m:<br>ORG 0000H<br>MOV P1, #0F0F                |                                                                                                                                                                                                                        | 3M |

### **SUMMER-18 EXAMINATION**

Subject Name: Micro controller Model Answer

17534 Subject Code: ; Key pressed branch from Port 0 CJNE A, #0F0H, CHECK1 SJMP START ; Branch to start CHECK1: ACALL DELAY ; Call delay 3M MOV A, P1 ; Read data from port 0 CPL A ; Complement A MOV PO, A ; Send data to LED AJMP START ; Jump to start DELAY: MOV R6,#20H ; Delay program NEXT1: MOV R7, #0FFH NEXT2: DJNZ R7, NEXT2 DJNZ R6, NEXT1 RET END

NOTE: Program may change. Please check the logic and understanding of students.

# SUMMER- 18 EXAMINATION Model Answer

Subject Name: Micro controller

Subject Code:

| Q.<br>No. | Sub      | Answers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Marking<br>Scheme  |

|-----------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|

| NO.       | Q.<br>N. |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Scheme             |

| 2         |          | Attempt any FOUR:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 16- Total<br>Marks |

|           | а        | Draw pin diagram of 8051 microcontroller.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 4M                 |

|           | Ans:     | 4 M for correct diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                    |

|           |          | P1.0       1       40       Vcc         P1.1       2       39       P0.0 (AD0)         P1.2       3       38       P0.1 (AD1)         P1.3       4       8051       37       P0.2 (AD2)         P1.4       5       36       P0.3 (AD3)         P1.5       6       35       P0.4 (AD4)         P1.6       7       34       P0.5 (AD5)         P1.7       8       33       P0.6 (AD6)         RST       9       32       P0.7 (AD7)         (RXD) P3.0       10       31       EAVPP         (TXD) P3.1       11       30       ALE/PROG         (INTT) P3.3       13       28       P2.7 (A15)         (TO P3.4       14       27       P2.6 (A14)         (T1) P3.5       15       26       P2.5 (A13)         (WF) P3.6       16       25       P2.4 (A12)         (RD) P3.7       17       24       P2.3 (A11)         XTAL2       18       23       P2.2 (A10)         XTAL1       19       22       P2.1 (A9)         GND       20       21       P2.0 (A8) | 4M                 |

|           | b        | Which pins of 8051 microcontroller are used for external memory interfacing with 8051?<br>State their functions.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 4M                 |

|           | Ans:     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                    |

|           | _        | The following pins of 8051 are used for external memory interfacing:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 1M each            |

|           |          | i) PSEN/:PSEN stands for —program store enable.∥ In an 8031-based system in which an                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                    |

|           |          | external ROM holds the program code, this pin is connected to the OE pin of the ROM.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                    |

|           |          | In other words, to access external ROM containing program code, the 8031/51 uses the                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                    |

|           |          | PSEN signal. When the EA pin is connected to GND, the 8031/51 fetches opcode from                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                    |

# SUMMER- 18 EXAMINATION Model Answer

Subject Name: Micro controller

Subject Code:

|           | machine cycles before it is allowed to go low.                                                                                                                           |            |

|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

|           | 3. In order for the RESET input to be effective, it must have a minimum duration of two machine cycles. In other words, the high pulse must be high for a minimum of two |            |

|           | values in the registers to be lost. It will set program counter to all 0s.                                                                                               |            |

|           | 2. This is often referred to as a power-on reset. Activating a power-on reset will cause all                                                                             |            |

|           | high pulse to this pin, the microcontroller will reset and terminate all activities.                                                                                     |            |

|           | 1. Pin 9 is the RESET pin. It is an input and is active high (normally low). Upon applying a                                                                             |            |

| ~113.     | Function of RESET:                                                                                                                                                       | explanatio |

| c<br>Ans: | Draw and explain reset circuit used for 8051 microcontroller.                                                                                                            | 4M<br>2M – |

|           | iv) RD(P3.7) and WR(P3.6): External data memory read and external data memory write.                                                                                     |            |

|           | pin should not be floated. (Should be connected to ground).                                                                                                              |            |

|           | all the instructions are fetched from the external memory. During normal operation, this                                                                                 |            |

|           | address the instructions are fetched from external program memory. If this pin is low,                                                                                   |            |

|           | executes instruction from the internal program memory till address OFFFH, beyond this                                                                                    |            |

|           | iii) <i>EA</i> : EA stands for External access pin and it is active low. When it is held high,                                                                           |            |

|           | chip.                                                                                                                                                                    |            |

|           | used for demultiplexing the address and data by connecting to the G pin of the 74LS373                                                                                   |            |

|           | latching the low byte of address during accesses to external memory. The ALE pin is                                                                                      |            |

|           | ii) ALE: ALE stands for address latch enable. It is an output pin and is active high for                                                                                 |            |

|           | on- chip ROM contains program code.                                                                                                                                      |            |

|           | is connected to VCC, these chips do not activate the PSEN pin. This indicates that the                                                                                   |            |

# SUMMER- 18 EXAMINATION Model Answer

Subject Name: Micro controller

17534

|      | M                                                                  | 10 uF<br>30 pF 11.0592 MHz 19<br>2 K 1 X2<br>30 pF 18<br>9 RST   | 2M –<br>Diagram |  |  |  |  |  |  |

|------|--------------------------------------------------------------------|------------------------------------------------------------------|-----------------|--|--|--|--|--|--|

|      | - Tuesday, 149y.14, 2015                                           | Robotics Club, YOR, WRC                                          |                 |  |  |  |  |  |  |

| d    | Draw the format of PS                                              | W register of $8051\mu$ C and state the function of each flag.   | 4M              |  |  |  |  |  |  |

|      |                                                                    |                                                                  |                 |  |  |  |  |  |  |

| Ans: | CY AC                                                              | F0 RS1 RS0 OV P                                                  |                 |  |  |  |  |  |  |

|      | CY PSW.7                                                           | Carry Flag.                                                      | 2M –            |  |  |  |  |  |  |

|      | AC PSW.6                                                           | Auxiliary carry flag.                                            | format          |  |  |  |  |  |  |

|      | F0 PSW.5                                                           | Available to the user for general purpose.                       |                 |  |  |  |  |  |  |

|      | RS1 PSW.4                                                          | Register bank selector bit 1.                                    |                 |  |  |  |  |  |  |

|      | RS0 PSW.3                                                          | Register bank selector bit 0.                                    |                 |  |  |  |  |  |  |

|      | OV PSW.2                                                           | Overflow flag.                                                   |                 |  |  |  |  |  |  |

|      | PSW.1                                                              | User- definable bit.                                             |                 |  |  |  |  |  |  |

|      | P PSW.0                                                            | Parity flag. Set/cleared by hardware each instruction cycle to   |                 |  |  |  |  |  |  |

|      |                                                                    | indicate and Odd/ even number of 1 bit in the accumulator.       |                 |  |  |  |  |  |  |

|      | 1. CY: Carry flag.                                                 |                                                                  |                 |  |  |  |  |  |  |

|      | 1. This flag is set whenever there is a carry out from the D7 bit. |                                                                  |                 |  |  |  |  |  |  |

|      | 2. The flag bit is affected                                        | ed after an 8 bit addition or subtraction.                       |                 |  |  |  |  |  |  |

|      | 3. It can also be set to                                           | 1 or 0 directly by an instruction such as SETB C and CLR C where |                 |  |  |  |  |  |  |

|      | SETB C stands for set bit carry and CLR C for clear carry.         |                                                                  |                 |  |  |  |  |  |  |

|      | SETEC Statius for set t                                            |                                                                  |                 |  |  |  |  |  |  |

|      | 2. AC: Auxiliary carry f                                           | lag                                                              |                 |  |  |  |  |  |  |

# SUMMER- 18 EXAMINATION Model Answer

Subject Name: Micro controller

Subject Code:

| <b>A</b> 113. | <b>i. Stack pointer:</b> The 8-bit stack pointer (SP) register is used to hold an internal RAM |                   |

|---------------|------------------------------------------------------------------------------------------------|-------------------|

| Ans:          |                                                                                                |                   |

|               | iv) Accumulator                                                                                |                   |

|               | iii) Program counter                                                                           |                   |

|               | ii) DPTR                                                                                       |                   |

|               | i) Stack pointer                                                                               |                   |

| 9             | Explain the function of following registers of 8051µC.                                         | 4M                |

|               |                                                                                                |                   |

|               | register contains an odd number of 1's, then P=1, P=0 if A has an even number of 1's.          |                   |

|               | 1. The parity flag reflects the number of 1s in the A (accumulator) register only. If the A    |                   |

|               | 6. P: Parity flag                                                                              |                   |

|               | signed arithmetic operations.                                                                  |                   |

|               | errors in unsigned arithmetic operations. The overflow flag is only used to detect errors in   |                   |

|               | high-order bit to overflow into the sign bit. In general, the carry flag is used to detect     |                   |

|               | This flag is set whenever the result of a signed number operation is too large, causing the    |                   |

|               | 5. OV: Overflow flag                                                                           |                   |

|               | 1 0 Bank2 (10H-17H)<br>1 1 Bank3 (18H-1FH)                                                     |                   |

|               | 0 1 Bank 1 (08H-0FH)                                                                           |                   |

|               | 0 0 Bank 0 (00H- 07H)                                                                          |                   |

|               | RS1 RS0 Space in RAM                                                                           |                   |

|               | of four registers banks in internal RAM.                                                       |                   |

|               | table. By writing zeroes and ones to these bits, a group of registers R0- R7 can be used out   |                   |

|               | 1. These two bits are used to select one of the four register banks n internal RAM in the      | 2M -<br>functions |

|               | 4. RS0, RS1: Register bank selects bits                                                        |                   |

|               | <b>3. F0:.</b> Available to the user for general purposes                                      |                   |

|               | arithmetic.                                                                                    |                   |

# SUMMER- 18 EXAMINATION Model Answer

Subject Name: Micro controller

Subject Code:

|      |                                                                                                                                                           | 1  |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|      | ii. DPTR : The DPTR register is made up of two registers named as DPH & DPL which are                                                                     |    |

|      | used to access any memory address that may be internal & external code access &                                                                           |    |

|      | external data access. The DPTR is under the program control & can also be specified as 16-                                                                |    |

|      | bit pointer as DPTR or by individual 8- bits as DPH & DPL. DPTR does have a single address                                                                |    |

|      | but the DPH is assigned the address as 82 H.                                                                                                              |    |

|      | iii. Program counter: The program counter (PC) is a 16-bit register. It is used to hold                                                                   |    |

|      | address of a byte in memory. Program instruction bytes are fetched from locations in                                                                      |    |

|      | memory that are addressed by PC. Program ROM may be on chip at addresses 0000H to                                                                         |    |

|      | OFFF H, external to the chip for addresses that exceeds OFFF h or totally external for all                                                                |    |

|      | addresses from 0000H to FFFF H. The PC is incremented automatically after every                                                                           |    |

|      | instruction byte is fetched. The PC is the only register that does not have any address.                                                                  |    |

|      | iv. Accumulator: It is also called as register A. It is an 8- bit register. The CPU of 8051 is                                                            |    |

|      | accumulator based hence it is used to hold the source operand and result of arithmetic                                                                    |    |

|      | operations like addition, subtraction, multiplication, division. However it is source as well                                                             |    |

|      | as destination for logical operations and data movement instructions. It can be used as a                                                                 |    |

|      | look up table pointer. It is also used in RAM expansion. It is specially used for rotate, parity                                                          |    |

|      | computation, testing for zero etc. It is bit accessible.                                                                                                  |    |

| f    | What is bus? Describe the function of address, data and control bus.                                                                                      | 4M |

| Ans: | A Bus is a set of physical connection used for communication between CPU and                                                                              |    |

|      | peripherals.                                                                                                                                              | 1M |

|      | There are three types of buses Address Bus, Data Bus and Control Bus                                                                                      |    |

|      | (1) Address Bus                                                                                                                                           |    |

|      | • The address bus is unidirectional over which the microcontroller sends an address                                                                       |    |

|      | code to the memory or input/output. The size of the address bus is specified by the                                                                       |    |

|      | number of bits it can handle.                                                                                                                             |    |

|      | • The more bits there are in the address bus, the more memory locations a                                                                                 |    |

|      | microcontroller can access. A 16-bit address bus is capable of addressing (64k)                                                                           |    |

|      | addresses.                                                                                                                                                |    |

|      |                                                                                                                                                           |    |

|      | • The more bits there are in the address bus, the more memory locations a microcontroller can access. A 16-bit address bus is capable of addressing (64k) |    |

# SUMMER- 18 EXAMINATION Model Answer

Subject Name: Micro controller

Subject Code:

| (2) Da |

|--------|

| •      |

| (3) Co |

| •      |

# SUMMER- 18 EXAMINATION Model Answer

Subject Name: Micro controller

17534

| Q.<br>No | Sub<br>Q. N. | Answers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Markin<br>g<br>Scheme |

|----------|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|

| 3        |              | Attempt any FOUR:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 16-<br>Total<br>Marks |

|          | а            | Explain the following directives with example.<br>i) ORG<br>ii) DB<br>iii) EQU<br>(iv) END                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 4M                    |

|          | Ans:         | ORG:-ORG stands for Origin<br>Syntax: ORG Address<br>The ORG directive is used to indicate the beginning of the address. The number<br>that comes after ORG can be either in hex or in decimal. If the number is not<br>followed by H, it is decimal and the assembler will convert it to hex. Some<br>assemblers use — .ORG (notice the dot) instead of —ORG for the origin directive.<br>DB:- (Define Byte)<br>Syntax: Label: DB Byte<br>Where byte is an 8-bit number represented in either binary, Hex, decimal or ASCII<br>form. There should be at least one space between label & DB. The colon (:) must<br>present after label. This directive can be used at the beginning of program. The<br>label will be used in program instead of actual byte. There should be at least one<br>space between DB & a byte.<br>EQU: Equate<br>It is used to define constant without occupying a memory location. | 1M<br>each            |

# SUMMER- 18 EXAMINATION Model Answer

Subject Name: Micro controller

Subject Code:

|      | Syntax: Label EQU Numeric value                                                                                                                                                                                                                                       |                   |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|

|      | By means of this directive, a numeric value is replaced by a symbol.                                                                                                                                                                                                  |                   |

|      | For e.g. MAXIMUM EQU 99 After this directive every appearance of the label —MAXIMUM in                                                                                                                                                                                |                   |

|      | the program, the assembler will interpret as number 99 (MAXIMUM=99).                                                                                                                                                                                                  |                   |

|      | END:                                                                                                                                                                                                                                                                  |                   |

|      | This directive must be at the end of every program meaning that in the source code anything                                                                                                                                                                           |                   |

|      | after the END directive is ignored by the assembler.                                                                                                                                                                                                                  |                   |

|      | This indicates to the assembler the end of the source file.                                                                                                                                                                                                           |                   |

|      | Once it encounters this directive, the assembler will stop interpreting program into machine                                                                                                                                                                          |                   |

|      | code.                                                                                                                                                                                                                                                                 |                   |

|      | e.g. END ; End of the program.                                                                                                                                                                                                                                        |                   |

| b    | State any four addressing mode of 8051 $\mu C$ and explain each with example.                                                                                                                                                                                         | 4M                |

|      |                                                                                                                                                                                                                                                                       |                   |

| Ans: | There are a number of addressing modes available to the 8051 instruction set, as follows:                                                                                                                                                                             | 1M                |

|      | 1. Immediate Addressing mode                                                                                                                                                                                                                                          | each              |

|      | 2. Register Addressing mode                                                                                                                                                                                                                                           | (½ M -<br>explana |

|      | 3. Direct Addressing mode                                                                                                                                                                                                                                             | tion,             |

|      | 4 Register Indirect addressing mode                                                                                                                                                                                                                                   | ½ M -             |

|      | 5. Relative Addressing mode                                                                                                                                                                                                                                           | exampl            |