(Autonomous)

(ISO/IEC - 27001 - 2005 Certified)

Subject Code: 17302 SUMMER – 15 EXAMINATION Model Answer

#### **Important Instructions to examiners:**

- 1) The answers should be examined by key words and not as word-to-word as given in the model answer scheme.

- 2) The model answer and the answer written by candidate may vary but the examiner may try to assess the understanding level of the candidate.

- 3) The language errors such as grammatical, spelling errors should not be given more Importance (Not applicable for subject English and Communication Skills.

- 4) While assessing figures, examiner may give credit for principal components indicated in the figure. The figures drawn by candidate and model answer may vary. The examiner may give credit for any

- equivalent figure drawn.

- 5) Credits may be given step wise for numerical problems. In some cases, the assumed constant values may vary and there may be some difference in the candidate's answers and model answer.

- 6) In case of some questions credit may be given by judgement on part of examiner of relevant answer based on candidate's understanding.

- 7) For programming language papers, credit may be given to any other program based on equivalent

(Autonomous) (ISO/IEC - 27001 - 2005 Certified)

**Model Answer** Subject Code : **17302 SUMMER – 15 EXAMINATION**

| Q.N | О  | Model Answer/Solution                                       |                                                       | Marks                           |        |

|-----|----|-------------------------------------------------------------|-------------------------------------------------------|---------------------------------|--------|

| 1   |    | Attempt any <u>SIX</u> of the following:                    |                                                       |                                 | 12     |

|     | a. | Symbol of FET and BJT                                       |                                                       |                                 | 1/2*4= |

|     |    | D   D                                                       | C                                                     | ] <b>c</b>                      | 02     |

|     |    |                                                             |                                                       | , /                             |        |

|     |    | $G \longrightarrow G \longrightarrow$                       | B                                                     | B—                              |        |

|     |    |                                                             | $\sim$                                                | ' `                             |        |

|     |    | , , , , , , , , , , , , , , , , , , ,                       | Ì                                                     | Ļ                               |        |

|     |    | N ch FET p ch FET                                           | NPN BJT                                               | PNP BJT                         |        |

|     | b  | Need of filter in Regulated power supply.                   |                                                       | 20.                             | 02     |

|     |    | The output of rectifier is not pure DC(pulsa                | ting DC), so to                                       | obtain pure DC signal filters   | 02     |

|     |    | are necessary (to remove harmonics at the ou                |                                                       |                                 |        |

|     | c  | Thermal runway:                                             |                                                       |                                 | 02     |

|     |    | The self-destruction of a transistor is known               | n as thermal ru                                       | nway. It is the cyclic process, |        |

|     |    | which destroys the transistor.                              |                                                       |                                 |        |

|     |    | As temperature increases, transistor leakage                |                                                       |                                 |        |

|     |    | the collector current I <sub>c</sub> due to which again jur | iction temperati                                      | ure increases and so on.        |        |

|     | d  | Pin diagram of IC 741 - opamp                               |                                                       |                                 | 02     |

|     | u  | 1 in diagram of 10 741 - opamp                              |                                                       |                                 | 02     |

|     |    | - Offset null 1 8                                           | ¬ NC                                                  |                                 |        |

|     |    |                                                             | _                                                     |                                 |        |

|     |    | Inverting input ☐ 2 7 7                                     | □ +VCC                                                |                                 |        |

|     |    |                                                             | _                                                     |                                 |        |

|     |    | Non inverting input $\square$ 3 4 6                         | □ output                                              |                                 |        |

|     |    | -VEE ☐ 4 1 5                                                | □ +Offset null                                        |                                 |        |

|     |    | VLL —                                                       | — Tonset nun                                          |                                 |        |

| 1   | e  | Symbol and truth table of                                   |                                                       |                                 | 1/2*4= |

|     |    | XNOR gate                                                   | A B Y                                                 | ,                               | 02     |

|     |    |                                                             | 0 0 1                                                 |                                 |        |

|     |    | Α ————————————————————————————————————                      |                                                       |                                 |        |

|     |    | ^                                                           | 0 1 0                                                 | , <u> </u>                      |        |

|     |    | В                                                           |                                                       |                                 |        |

|     |    | Б                                                           | 1 0 0                                                 |                                 |        |

|     |    |                                                             | 1 1 1                                                 |                                 |        |

|     |    |                                                             |                                                       |                                 |        |

|     |    | NAND gate                                                   |                                                       |                                 |        |

|     |    |                                                             |                                                       |                                 |        |

|     |    |                                                             | A B Y                                                 |                                 |        |

|     |    | ·· —                                                        | 0 0 1                                                 |                                 |        |

|     |    | 1 0                                                         | $\begin{array}{c ccccccccccccccccccccccccccccccccccc$ |                                 |        |

|     |    | ь 🗀                                                         | 1 0 1                                                 |                                 |        |

|     |    |                                                             | 1 1 0                                                 |                                 |        |

|     |    |                                                             | · · ·                                                 | <del></del>                     |        |

|     |    |                                                             |                                                       |                                 |        |

(Autonomous)

(ISO/IEC - 27001 - 2005 Certified)

Subject Code : **17302 Model Answer SUMMER – 15 EXAMINATION**

| 1 | f | Any four solid state devices                                                    | 1/2*4=02 |

|---|---|---------------------------------------------------------------------------------|----------|

|   |   | I) Diode                                                                        |          |

|   |   | II) Transistor (BJT)                                                            |          |

|   |   | III) UJT                                                                        |          |

|   |   | IV) FET                                                                         |          |

|   |   | V) Any other suitable and relevant solid state devices may also                 |          |

|   |   | considered                                                                      |          |

|   | g | Mechatronics: - It is a multidisciplinary approach to product and manufacturing | 02       |

|   |   | system design. Mechatronics is the synergistic integration of mechanical        |          |

|   |   | engineering with electronics and intelligent computer control in designing,     |          |

|   |   | manufacturing process and production. It helps develop atomized and efficient   |          |

|   |   | manufacturing/production systems to produce high quality products.              |          |

|   |   |                                                                                 |          |

|   | h | Types of real time Mechatronics systems.                                        | 1/2*4=02 |

|   |   | 1) Programmable logic controllers (PLC)                                         |          |

|   |   | 2) Computer numerical control system (CNC)                                      |          |

|   |   | <ul><li>3) SCADA system</li><li>4) HMI</li></ul>                                |          |

|   |   | 4) HMI                                                                          |          |

|   |   | Any other relevant Mechatronics systems may also considered.                    |          |

| 1 | В | Attempt any Two                                                                 | 08       |

|   | a | Bridge wave rectifier and its waveforms                                         | 02+02    |

|   |   | P 5                                                                             |          |

|   |   | M, D <sub>1</sub>                                                               |          |

|   |   |                                                                                 |          |

|   |   |                                                                                 |          |

|   |   | 7230V 9 6 703 XD2                                                               |          |

|   |   | Vout                                                                            |          |

|   |   | Towns frames                                                                    |          |

|   |   | (Step-down)                                                                     |          |

|   |   | Vin                                                                             |          |

|   |   | Vin                                                                             |          |

|   |   |                                                                                 |          |

|   |   |                                                                                 |          |

|   |   | Vout O O O O t                                                                  |          |

|   |   |                                                                                 |          |

|   |   | <u> </u>                                                                        |          |

|   |   |                                                                                 |          |

|   |   |                                                                                 |          |

|   |   |                                                                                 |          |

|   |   |                                                                                 |          |

|   |   |                                                                                 |          |

(Autonomous)

(ISO/IEC - 27001 - 2005 Certified) **SUMMER – 15 EXAMINATION**

Subject Code : **17302 Model Answer**

| Q.N | О | Model Answer/Solution                                                                                                                                                                                                                                                                                    | Marks |

|-----|---|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

| 1   | В |                                                                                                                                                                                                                                                                                                          |       |

|     | b | Working of inverting amplifier.                                                                                                                                                                                                                                                                          | 02+02 |

|     |   | When input is given at inverting terminal and non inverting terminal is grounded then the configuration is known as inverting mode of op-amp.  Rf is a feedback resistor and R1 is input resistor. The gain of inverting mode of op-amp is G = - Rf/R1  The negative sign indicated inversion at output. |       |

|     | С | Real time Mechatronics systems and its advantages and disadvantages  A mechatronic system which performs various functions or operations with respect to time is referred as real time Mechatronics system. e.g. PLC,SCADA,HMI etc                                                                       | 02 +  |

|     |   | Advantages: 1 Feet enough of response                                                                                                                                                                                                                                                                    |       |

|     |   | Advantages: - 1. Fast speed of response                                                                                                                                                                                                                                                                  |       |

|     |   | 2. High accuracy                                                                                                                                                                                                                                                                                         |       |

|     |   | 3. More flexible                                                                                                                                                                                                                                                                                         | 01    |

|     |   | 4. Overall cost is low                                                                                                                                                                                                                                                                                   | +     |

|     |   | <b>Disadvantages:-</b> 1. More complex 2. Need of expert                                                                                                                                                                                                                                                 |       |

|     |   | 3. Difficult to maintain                                                                                                                                                                                                                                                                                 | 01    |

|     |   | 4. Due to mechanical parts more Noisy system                                                                                                                                                                                                                                                             |       |

|     |   | Any suitable and relevant point may also consider.                                                                                                                                                                                                                                                       |       |

|     |   |                                                                                                                                                                                                                                                                                                          |       |

|     |   |                                                                                                                                                                                                                                                                                                          |       |

|     |   |                                                                                                                                                                                                                                                                                                          |       |

# MAHARASHTRA STATE BOARD OF TECHNICAL EDUCATION (Autonomous) (ISO/IEC - 27001 - 2005 Certified)

Subject Code : **17302 SUMMER – 15 EXAMINATION**  **Model Answer**

| Q.No | 0 | Model Answer/Solution                                                                                                                                                                                                                                                                                                                                                                                                                                         | Marks    |

|------|---|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| 2    |   | Attempt any four                                                                                                                                                                                                                                                                                                                                                                                                                                              | 16       |

|      | a | Biasing:- It is the process of selecting the value of collector current I <sub>C</sub> and Collector to emitter voltage V <sub>ce</sub> .(selecting position of operating point of transistor on DC load line)  To use transistor as an amplifier it should be always operated in active region so we have to provide proper biasing to the transistor.  Voltage divider biasing for BJT  R <sub>1</sub> § R <sub>2</sub> provides  Voltage divider  Blasing. | 02+02    |

|      | b | Two stage RC coupled amplifier                                                                                                                                                                                                                                                                                                                                                                                                                                | 02+01+01 |

|      |   | CIA CE WREL TCE2                                                                                                                                                                                                                                                                                                                                                                                                                                              |          |

|      |   | Advantages:- More bandwidth Simple in construction Low cost Disadvantages:- Overall gain reduces Not suitable for low frequency signals. Any other suitable and relevant advantages and disadvantages may also considered.                                                                                                                                                                                                                                    |          |

(Autonomous)

(ISO/IEC - 27001 - 2005 Certified)

Subject code: 17302 SUMMER – 15 EXAMINATION <u>Model Answer</u>

| Q.No | Model Answer/Solution                                                                                                                                                                                                                                                                                                           |                                                                                                  |                                      | Marks |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------|--------------------------------------|-------|

| 2 c  | Ideal characteristics of Op-a                                                                                                                                                                                                                                                                                                   | mp                                                                                               |                                      | 01*04 |

|      |                                                                                                                                                                                                                                                                                                                                 |                                                                                                  |                                      |       |

|      | Cha                                                                                                                                                                                                                                                                                                                             | aracteristics                                                                                    | Ideal value                          |       |

|      | Ope                                                                                                                                                                                                                                                                                                                             | en loop gain                                                                                     | infinity                             |       |

|      | Inp                                                                                                                                                                                                                                                                                                                             | ut impedance                                                                                     | infinity                             |       |

|      | Bar                                                                                                                                                                                                                                                                                                                             | ndwidth                                                                                          | infinity                             |       |

|      | Sle                                                                                                                                                                                                                                                                                                                             | w rate                                                                                           | infinity                             |       |

|      | Out                                                                                                                                                                                                                                                                                                                             | put impedance                                                                                    | zero                                 |       |

|      | CM                                                                                                                                                                                                                                                                                                                              | IRR                                                                                              | infinity                             |       |

|      | Any other relevant characterist                                                                                                                                                                                                                                                                                                 | tics may also be cons                                                                            | sidered                              |       |

| d    | Block diagram of IC 555                                                                                                                                                                                                                                                                                                         | - 18(+vc)                                                                                        |                                      | 02+02 |

|      | Dischange 7                                                                                                                                                                                                                                                                                                                     | Cu                                                                                               |                                      |       |

|      | IC555 consist of three 5KΩ result consist of Two comparators. Upper comparator Lower comparator Upper comparator has reference reference voltage of Vcc/3. Voltage at pin no. 2 and 6 is all produced which will either SE It also consist of Two transistor Q1 is npn which is used to discuss Q2 is pnp and used to reset the | ce voltage of 2Vcc/3 ways compared with T the FF or RESET to ors Q1 and Q2 charge external capac | these voltages and output is the FF. |       |

| e    |                                                                                                                                                                                                                                                                                                                                 | ch generates oscilla                                                                             | tions (waveforms of desired          | 02    |

(Autonomous)

(ISO/IEC - 27001 - 2005 Certified)

Subject Code : **17302 Model Answer SUMMER – 15 EXAMINATION**

| Q.No | 0 | Model Answer/Solution                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Marks |

|------|---|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

| 2    | e | Continue  Barkhausen's Criteria:  Barkhausen's criterion is applicable for oscillators.  According to this criteria the circuit has to satisfy two conditions  First:- the total phase shift given by the circuit should be $360^{\circ}$ or $0^{\circ}$ . And Second:- The factor $A\beta$ should be less than equal to one.                                                                                                                                               | 02    |

|      | f | Multiplexer:- a device which has many inputs and only one output, the particular input is selected by select inputs. The no. of select inputs are depends upon number of inputs and can be calculated as $2^{N} >= M$ Where N= number of select inputs $M = \text{number of inputs}$ Logical symbol of 4:1 multiplexer $\text{For 4:1 multiplexer, it requires 2 select inputs.}$ $  \text{INPUTs} $ $  \text{Chip Select/} $ $  \text{Strobe i/p} $ $  \text{Strobe i/p} $ | 02+02 |

|      |   | Selec t inputs                                                                                                                                                                                                                                                                                                                                                                                                                                                              |       |

| 3    |   | Attempt any Four                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 16    |

|      | a | BJT as an amplifier:-                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 02    |

Subject Code : **17302**

#### MAHARASHTRA STATE BOARD OF TECHNICAL EDUCATION

(Autonomous)

(ISO/IEC - 27001 - 2005 Certified)

SUMMER – 15 EXAMINATION Model Answer

Model Answer/Solution Q.N Mark o 3 Continue... 02 a When transistor is operated in active region it acts as an amplifier. And CE configuration is most widely used configuration because it is more advantageous than other configurations. Input is applied at base terminal and capacitor Cin is used to pass pure ac signal. Voltage divider biasing is used due to more stability. And feedback used in amplifier is negative feedback. In CE configuration transistor provides 180degree phase shift to voltage. Half adder circuit h Half Adder - A combinational circuit used to perform addition of two binary bits and produces Sum and Carry bits as a result. Logical Circuit diagram-Α SUM Sum 02 Half adder dig. В Carry Carry Truth Table В Sum Carry 0 0 0 01TT 1 1 0 0 1 0 1 0 1 1 0 1 Explanation of truth table 01 Exp. Compare microprocessor with microcontroller. 01\*4 Microcontroller **Parameter** Microprocessor It is a CPU It consists of CPU, RAM, Components ROM, I/O ports, timer, Converters Access time High Less Number of opcodes Less More Hardware required RAM, ROM, I/O ports, timer, In built converters externally. Any other suitable and relevant point is also considered.

(Autonomous) (ISO/IEC - 27001 - 2005 Certified)

Subject code: 17302 SUMMER – 15 EXAMINATION

**Model Answer**

| Q.N<br>o | Model Answer/Solution                                                                                                                                                                                                                                          | Marks                                   |  |  |  |

|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|--|--|--|

| 3 d      | <b>Decoder:</b> -It is a combination logic circuit used to select a device or decode. Decoders consist of number of inputs (N) and number of output(M) and both are related as $2^N >= M$ The standard decoders are 1:2,2:4,3:8 and so on 3:8 decoder          |                                         |  |  |  |

|          | Inputs Outputs.  A B C To TI TZ TS TA TS TO TT TO TE                                                                                                                                                                       |                                         |  |  |  |

| e        | For example: - Thermocouple converts temperature into voltage or C type                                                                                                                                                                                        | 02one<br>example<br>each                |  |  |  |

|          | Secondary Transducer: In this type of Transducer, energy conversion is two times i.e. from physical to, To suitable {may another physical} and suitable to required one{Electrical or Mechanical}.                                                             | +                                       |  |  |  |

|          | For example: - RTD or Thermister converts temperature into change in resistance and change in resistance is converted into voltage or C type Bourdon tube converts pressure into Displacement and displacement is converted into electrical signal using LVDT. |                                         |  |  |  |

|          | Any other relevant examples may also be considered                                                                                                                                                                                                             | 02<br>One /each                         |  |  |  |

|          | Marks are given depending upon examples only.                                                                                                                                                                                                                  | one /eacl.                              |  |  |  |

| f        | Block diagram of CNC system:-                                                                                                                                                                                                                                  | 2M for<br>Block                         |  |  |  |

|          | Tape NC Microcomp Computer reader program uter hardware for initial Storage (software interface                                                                                                                                                                | diagram<br>+ 2M for<br>Expla-<br>nation |  |  |  |

|          | Any suitable and relevant block diagram and explanation may also be considered.                                                                                                                                                                                | 1                                       |  |  |  |

(Autonomous)

(ISO/IEC - 27001 - 2005 Certified)

**Model Answer** Subject Code : **17302 SUMMER – 15 EXAMINATION**

| No | Model Answer/Solution                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Mark |

|----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| a  | Attempt any Four Functional block diagram of AVCS                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 16   |

|    | Vehicle States of Motion  Vehicle States of Motion  Vehicle States of Motion  Vehicle States of Motion  Driving Behavior  Environmental Information  Driver's Characteristics Characteristics Dynamics  Identification of Vehicle States of Motion  Subsystem  Vehicle States of Motion  Student may draw the different functional diagram, please consider if it is logically |      |

| b  | BJT as a switch  Transistor as a switch  Vin = 0 Transistor is off switch  Vin = +v Transistor is off switch  Dre may take off from collector or emitter                                                                                                                                                                                                                                                                                                                                                     | 02+0 |

(Autonomous) (ISO/IEC - 27001 - 2005 Certified)

Subject code : **17302 Model Answer SUMMER – 15 EXAMINATION**

| Q.N | O. | Model Answer/Solution                                                              | Marks   |

|-----|----|------------------------------------------------------------------------------------|---------|

| 4   | С  | Ladder diagram for start stop logic with one input push button for start and one   |         |

| •   |    | push button for stop and output motor to activate solenoid valve.                  |         |

|     |    | publication for stop and output motor to activate solehold varve.                  | 04      |

|     |    | S1 – Stop button                                                                   |         |

|     |    | S2 – Start button                                                                  |         |

|     |    |                                                                                    |         |

|     |    | S1 S2 M V M- motor<br>V- Solenoid valve                                            |         |

|     |    | v-Solellold valve                                                                  |         |

|     |    |                                                                                    |         |

|     |    |                                                                                    |         |

|     |    |                                                                                    |         |

|     |    | Student may draw different ladder discream as non his locia if locia is somest it  |         |

|     |    | Student may draw different ladder diagram as per his logic, if logic is correct it |         |

|     | .1 | may also be considered                                                             | 02 : 02 |

|     | d  | Data logger                                                                        | 02 +02  |

|     |    | In industries and process plants, data loggers are becoming very popular to        |         |

|     |    | monitor, display, measure, store and control different process variables.          |         |

|     |    | Data is nothing but output from different transducers and log means permanent      |         |

|     |    | storage of this data. The data logger handles digital information.(The system      |         |

|     |    | which stores the output of different transducers in a process plant.)              |         |

|     |    | Applications of data logger                                                        |         |

|     |    | Data loggers are widely used in power generation plants, petrochemical             |         |

|     |    | industries, oil refineries industriesetc.                                          |         |

|     |    | Any other suitable and relevant applications may also considered.                  |         |

|     | 2  | DAC Data Acquisition Systems. The function of DAC is to collect the input          |         |

|     | e  | <b>DAS</b> - Data Acquisition System:- The function of DAS is to collect the input | 02      |

|     |    | data efficiently, accurately, simultaneously to store and display the data. It     | 02      |

|     |    | consist of sensor or transducer associated with signal conditioning element,       |         |

|     |    | multiplexer circuit, data conversion, data transmission and final storage element  |         |

|     |    | and display unit.                                                                  |         |

|     |    | Types of DAS                                                                       |         |

|     |    | Single channel DAS                                                                 |         |

|     |    | Multi channel DAS                                                                  | 0.2     |

|     |    | Application of DAS                                                                 | 02      |

|     |    | In instrumentation system of industries for measurement of Temperature,            |         |

|     |    | pressure, velocity, thickness etc.                                                 | 0.0     |

|     | f  | Opto-coupler: It is a combination of photo (light) source and photo sensor         | 02      |

|     |    | (detector) in a same package. They are used to couple the signal from one point    |         |

|     |    | to other point optically with electrical isolation.                                |         |

|     |    | APPLICATIONS:-                                                                     |         |

|     |    | I) used in burglar alarm circuits                                                  |         |

|     |    | II) used in batch counter/ object counter                                          |         |

|     |    | III) in fire alarm circuits                                                        | 02      |

|     |    | IV) Any other relevant application may also considered. (any two)                  |         |

Subject Code : **17302**

#### MAHARASHTRA STATE BOARD OF TECHNICAL EDUCATION

(Autonomous)

(ISO/IEC - 27001 - 2005 Certified)

SUMMER — 15 EXAMINATION

**Model Answer**

#### Q. 5 Attempt any four

#### a) What is a ADC and DAC? List out its types

Ans: ADC & its type (2 marks), DAC & its Types (2 marks)

**ADC** (Analog to Digital Convertor): An analog-to-digital converter (ADC, A/D, or A to D) is a device that converts a continuous physical quantity to a digital number that represents the quantity's amplitude.

### Types of ADC: (any 2)

- Flash type

- Tracking or servo type

- Single slop

- Counter type

- Successive approximation

- Dual slope

**DAC** ( **Digital to Analog convertor**): A digital-to-analog converter (*DAC*, D/A, D2A or D-to-A) is a function that converts digital data (usually binary) into an analog signal (current, voltage, or electric charge).

#### **Types of DAC**

- Binary weighted register

- R-2R ladder

#### b) Compare between analog and digital transducer (any 4 points) 1 mark to each point

| Analog Transducer                                                                                                  | Digital Transducer                                                               |  |

|--------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|--|

| Its output is in the form of analog                                                                                | Its output is in the form of digital                                             |  |

| Produces the output which is tend to be very small in value from a few mico-volts (uV) to several milli-volts (mV) | produce a <u>Binary</u> output signal in the form of a logic "1" or a logic "0", |  |

| Usually have a slow response and/or low accuracy.                                                                  | Comparatively high accurate and fast in response.                                |  |

| Examples: Thermocouple, LVDT, Strain gauge                                                                         | Examples: Shaft encoder, Digital Tachometer                                      |  |

(Autonomous)

(ISO/IEC - 27001 - 2005 Certified)

Subject code: 17302 SUMMER – 15 EXAMINATION <u>Model Answer</u>

## c) Differentiate between intrinsic and extrinsic semiconductor ( any 4 points) 1 mark to each point

| Intrinsic Semiconductor                                                    | Extrinsic Semiconductor                                                                                                    |

|----------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|

| It is pure semi-conducting material and no impurity atoms are added to it. | It is prepared by doping a small quantity of impurity atoms to the pure semi-conducting material.                          |

| Its electrical conductivity is low.                                        | Its electrical conductivity is high.                                                                                       |

| Its electrical conductivity is a function of temperature alone.            | Its electrical conductivity depends upon the temperature as well as on the quantity of impurity atoms doped the structure. |

| Examples: crystalline forms of pure silicon and germanium.                 | Examples: n-type, p-type                                                                                                   |

d) Define current gain in CB and CE configuration. State relationship between them.

Definition 2 marks and relation between them 2 marks

Current gain in CB: The current gain for the common-base configuration is defined as the change in collector current divided by the change in emitter current. It is denoted by  $\alpha$

Current gain in CE: The current gain for the common-Emitter configuration is defined as the change in collector current divided by the change in base current. It is denoted by  $\beta$

**Relation between them:**

$$\alpha = \frac{\beta}{\beta + 1}$$

or  $\alpha = \beta(1 - \alpha)$

$$\beta = \frac{\alpha}{1-\alpha}$$

or  $\beta = \alpha(1+\beta)$

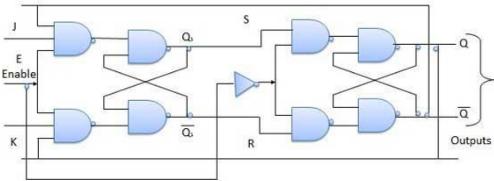

e) Explain the working of master slave J.K. Flip Flop.

(working 2 marks, diagram and truth table 2 marks)

The input signals J and K are connected to the gated "master" SR flip flop which "locks" the input condition while the clock (Clk) input is "HIGH" at logic level "1". As the clock input of the "slave" flip flop is the inverse (complement) of the "master" clock input, the "slave" SR flip flop does not toggle. The outputs from the "master" flip flop are only "seen" by the gated "slave" flip flop when the clock input goes "LOW" to logic level "0".

(Autonomous) (ISO/IEC - 27001 - 2005 Certified)

Subject code: 17302 SUMMER – 15 EXAMINATION <u>Model Answer</u>

When the clock is "LOW", the outputs from the "master" flip flop are latched and any additional changes to its inputs are ignored. The gated "slave" flip flop now responds to the state of its inputs passed over by the "master" section.

Then on the "Low-to-High" transition of the clock pulse the inputs of the "master" flip flop are fed through to the gated inputs of the "slave" flip flop and on the "High-to-Low" transition the same inputs are reflected on the output of the "slave" making this type of flip flop edge or pulse-triggered.

Then, the circuit accepts input data when the clock signal is "HIGH", and passes the data to the output on the falling-edge of the clock signal. In other words, the **Master-Slave JK**Flip flop is a "Synchronous" device as it only passes data with the timing of the clock signal.

#### **Truth Table**

|   | Inputs |   |     | puts | Comments  |

|---|--------|---|-----|------|-----------|

| E | J      | К | Qna | Qua  | Comments  |

| 1 | 0      | 0 | Q.  | Q.   | No change |

| 1 | 0      | 1 | 0   | 1    | Rset      |

| 1 | 1      | 0 | 1   | 0    | Set       |

| 1 | 1      | 1 | Q.  | Q.   | Toggle    |

#### f) List applications of photodiode and phototransistor.

#### **Applications of photodiode any 4** ( 2 marks)

- Cameras

- Medical devices

- Safety equipment

- Optical communication devices

- Position sensors

- Bar code scanners

(Autonomous)

(ISO/IEC - 27001 - 2005 Certified)

Subject code: 17302 SUMMER – 15 EXAMINATION <u>Model Answer</u>

- Automotive devices

- Surveying instruments

#### **Applications of phototransistor any 4 (2 marks)**

- Punch-card readers.

- Security systems

- Encoders measure speed and direction

- IR detectors photo

- electric controls

- Computer logic circuitry.

- Relays

- Lighting control (highways etc)

- Level indication

- Counting systems

#### Q 6. Attempt any four:

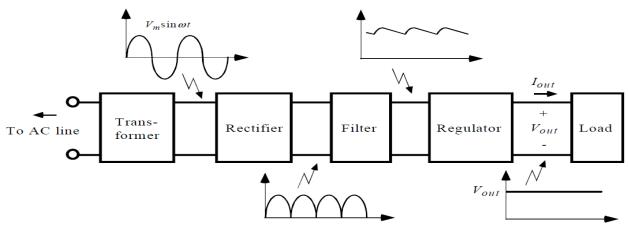

#### a) Draw block diagram of regulated power supply. State function of each block

Block diagram 2 marks and functions 2 marks

Components of a typical linear power supply

**Step Down Transformer**: A step down transformer will step down the voltage from the ac mains to the required voltage level. The turn's ratio of the transformer is so adjusted such as to obtain the required voltage value. The output of the transformer is given as an input to the rectifier circuit.

**Rectification:** Rectifier is an electronic circuit consisting of diodes which carries out the rectification process. Rectification is the process of converting an alternating voltage or current into corresponding direct (dc) quantity. The input to a rectifier is ac whereas its output is unidirectional pulsating dc. Usually a full wave rectifier or a bridge rectifier is used to rectify both the half cycles of the ac supply (full wave rectification).

(Autonomous)

(ISO/IEC - 27001 - 2005 Certified) SUMMER – 15 EXAMINATION

**Model Answer**

Subject Code : **17302**

**Filter**: The rectified voltage from the rectifier is a pulsating dc voltage having very high ripple content. But this is not we want, we want a pure ripple free dc waveform. Hence a filter is used. Different types of filters are used such as capacitor filter, LC filter, Choke input filter,  $\pi$  type filter. **Regulator**: This is the last block in a regulated DC power supply. The output voltage or current will change or fluctuate when there is change in the input from ac mains or due to change in load current at the output of the regulated power supply or due to other factors like temperature changes. This problem can be eliminated by using a regulator. A regulator will maintain the output constant even when changes at the input or any other changes occur.

#### b) Explain load and line regulation in regulated power supply.

#### **Load regulation (2 marks)**

Load regulation is the capability to maintain a constant output voltage despite changes in the supply's load current from no load to full load.

$$\% \text{Load Regulation} = 100\% \, \frac{V_{min-load} - V_{max-load}}{V_{nom-load}}$$

#### Line regulation (2 marks)

It is the change in the regulated load voltage due to change in line voltage in a specified range of

230V ±10% at constant load current.

% Line regulation = VLH – VLL/ Vnom \* 100

#### c) Compare LC and RC oscillators (any 4 points) 1 mark each

| LC oscillator                       | RC oscillator                       |  |  |

|-------------------------------------|-------------------------------------|--|--|

| Frequency of oscillation depends on | Frequency of oscillation depends on |  |  |

| value of L and C                    | value of R and C                    |  |  |

| They are used at high frequency     | They are used at low and medium     |  |  |

|                                     | frequency                           |  |  |

| Examples: Phase shift, Wien bridge  | Examples : Hartley , colpitt's.     |  |  |

| Applications: low and medium        | Applications: radio, TV.            |  |  |

| frequency range signal generators   |                                     |  |  |

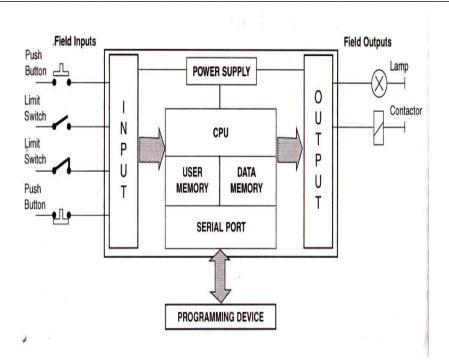

#### d) Draw block diagram of PLC. State function of each block.

Block diagram 2 marks, functions 2 marks

(Autonomous)

(ISO/IEC - 27001 - 2005 Certified)

Subject code: 17302 SUMMER – 15 EXAMINATION <u>Model Answer</u>

A Programmable Controller is a specialized computer. Since it is a computer, it has all the basic component parts that any other computer has; a Central Processing Unit, Memory, Input Interfacing and Output Interfacing. A typical programmable controller block diagram is shown above.

#### • The Central Processing Unit (CPU) is the control portion of the PLC.

- 1. It interprets the program commands retrieved from memory and acts on those commands.

- 2. In present day PLC's this unit is a microprocessor based system.

- 3. The CPU is housed in the processor module of modularized systems.

#### • Memory in the system is generally of two types; ROM and RAM.

- 1. The ROM memory contains the program information that allows the CPU to interpret and act on the Ladder Logic program stored in the RAM memory.

- 2. RAM memory is generally kept alive with an on-board battery so that ladder programming is not lost when the system power is removed.

- 3. This battery can be a standard dry cell or rechargeable nickel-cadmium type.

- 4. Newer PLC units are now available with Electrically Erasable Programmable Read Only Memory (EEPROM) which does not require a battery.

#### Input units

- 1. The input section can accept discrete or analog signals of various voltage and current levels.

- 2. Present day controllers offer discrete signal inputs of both AC and DC voltages from TTL to 250 VDC and from 5 to 250 VAC.

## MAHARASHTRA

Subject Code : **17302**

#### MAHARASHTRA STATE BOARD OF TECHNICAL EDUCATION

(Autonomous)

(ISO/IEC - 27001 - 2005 Certified)

SUMMER - 15 EXAMINATION Model Answer

3. Analog input units can accept input levels such as ±10 VDC, ±5 VDC and 4-20 ma.

- 3. Analog input units can accept input levels such as ±10 VDC, ±5 VDC and 4-20 ma current loop values.

- 4. Discrete input units present each input to the CPU as a single 1 or 0 while analog input units contain analog to digital conversion circuitry and present the input voltage to the CPU as binary number normalized to the maximum count available from the unit.

- 5. The number of bits representing the input voltage or current depends upon the resolution of the unit.

- 6. This number generally contains a defined number of magnitude bits and a sign bit.

- 7. Register input units present the word input to the CPU as it is received (Binary or BCD).

- Output units operate much the same as the input units with the exception that the unit is either sinking (supplying a ground) or sourcing (providing a voltage) discrete voltages or sourcing analog voltage or current.

- 1. These output signals are presented as directed by the CPU. The output circuit of discrete units can be transistors for TTL and higher DC voltage or Triacs for AC voltage outputs.

- 2. For higher current applications and situations where a physical contact closure is required, mechanical relay contacts are available.

- 3. These higher currents, however, are generally limited to about 2-3 amperes.

- 4. The analog output units have internal circuitry which performs the digital to analog conversion and generates the variable voltage or current output.

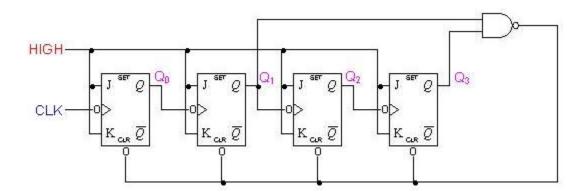

#### e) Draw and explain the working of decade counter using JK Flip Flop.

Draw counter 2 marks, explaination with truth table 2 marks

(Autonomous)

(ISO/IEC - 27001 - 2005 Certified)

Subject code: 17302 SUMMER – 15 EXAMINATION <u>Model Answer</u>

#### **Decade Counter Truth Table**

| Clock<br>Count | Outpu                                   | Output bit Pattern |    |    | Decimal |  |

|----------------|-----------------------------------------|--------------------|----|----|---------|--|

|                | QD                                      | QC                 | QB | QA | Value   |  |

| 1              | 0                                       | 0                  | 0  | 0  | 0       |  |

| 2              | 0                                       | 0                  | 0  | 1  | 1       |  |

| 3              | 0                                       | 0                  | 1  | 0  | 2       |  |

| 4              | 0                                       | 0                  | 1  | 1  | 3       |  |

| 5              | 0                                       | 1                  | 0  | 0  | 4       |  |

| 6              | 0                                       | 1                  | 0  | 1  | 5       |  |

| 7              | 0                                       | 1                  | 1  | 0  | 6       |  |

| 8              | 0                                       | 1                  | 1  | 1  | 7       |  |

| 9              | 1                                       | 0                  | 0  | 0  | 8       |  |

| 10             | 1                                       | 0                  | 0  | 1  | 9       |  |

| 11             | Counter Resets its Outputs back to Zero |                    |    |    |         |  |

#### **Working:**

This type of asynchronous counter counts upwards on each trailing edge of the input clock signal starting from 0000 until it reaches an output 1001 (decimal 9). Both outputs QA and QD are now equal to logic "1". One the application of the next clock pulse, the output from the NAND gate changes state from logic "1" to a logic "0" level.

As the output of the NAND gate is connected to the CLEAR (CLR) inputs of all the J-K Flip-flops, this signal causes all of the Q outputs to be reset back to binary 0000 on the count of 10. As outputs QA and QD are now both equal to logic "0" as the flip-flops have just been reset, the output of the NAND gate returns back to a logic level "1" and the counter restarts again from 0000.

#### f) State important features of 8051 microcontroller (any 8) ½ marks each

- 4 KB on chip program memory.

- 128 bytes on chip data memory(RAM)

- 4 register banks.

- 128 user defined software flags.

- 8-bit data bus

- 16-bit address bus

- 16 bit timers.

- 3 internal and 2 external interrupts.

- Bit as well as byte addressable RAM area of 16 bytes.

- Four 8-bit ports

- 16-bit program counter and data pointer.